XCV200-6FG456C FPGA: ویژگی ها ، مشخصات ، برنامه نویسی و برنامه ها

XCV200-6FG456C یک FPGA قدرتمند (آرایه دروازه قابل برنامه ریزی) از سری AMD Xilinx Virtex® است.این راهنما ویژگی های آن ، طرح پین ، مراحل برنامه نویسی و کاربردهای آن را توضیح می دهد.این FPGA با داشتن قدرت پردازش بالا ، گزینه های طراحی انعطاف پذیر و قابلیت های ورودی/خروجی قوی (I/O) ، به ساخت سیستم های دیجیتالی سریع و قابل اعتماد کمک می کند.این که آیا شما روی شبکه ، سیستم های کنترل یا الکترونیک سفارشی کار می کنید ، این راهنما به شما کمک می کند تا درک کنید که چگونه می توان از XCV200-6FG456C در پروژه های شما استفاده کرد.کاتالوگ

نمای کلی XCV200-6FG456C

در XCV200-6FG456C یک مدل قابل توجه در خانواده AMD Xilinx Virtex® FPGA است که به منظور ارائه راه حل های منطقی قابل برنامه ریزی برای سیستم های دیجیتالی پیچیده طراحی شده است.این تراشه خاص تقریباً 236،666 دروازه سیستم را در بر می گیرد و دارای 1،176 بلوک منطق قابل تنظیم (CLB) و 5،292 سلول منطقی است.همچنین شامل 57،344 بیت کل RAM است و از 284 پین I/O پشتیبانی می کند ، که در یک بسته آرایه شبکه توپ خوب 456 توپ (FBGA) قرار دارد و اندازه آن 23mm x 23mm است.این مدل با ولتاژ اسمی 2.5 ولت ، با دامنه 2.375 ولت تا 2.625 ولت کار می کند و می تواند در محدوده دمای 0 درجه سانتیگراد تا 85 درجه سانتیگراد عمل کند.سری گسترده تر Virtex® به طیف وسیعی از برنامه های کاربردی با تراکم از 50،000 تا بیش از 1 میلیون دروازه سیستم و نرخ ساعت سیستم تا 200 مگاهرتز می پردازد.این از استانداردهای متعدد I/O از جمله LVTTL ، LVCMOS و PCI در میان دیگران پشتیبانی می کند.ویژگی هایی مانند حلقه های قفل شده تاخیر (DLL) ، بلوک های منطقی قابل تنظیم با حافظه تعبیه شده و منطق حمل اختصاصی برای عملیات حسابی باعث افزایش عملکرد آن می شوند.ساخته شده با استفاده از یک فرآیند فلزی 5 لایه 0.22 میکرومتر ، خانواده Virtex® عملکرد و قابلیت اطمینان را تضمین می کند.

اگر به دنبال ادغام فناوری FPGA درجه یک در محصولات یا سیستم های خود هستید ، خرید XCV200-6FG456C به صورت عمده با ما یک حرکت هوشمندانه است.این استانداردهای صنعت را رعایت می کند و شما را از نیازهای آینده فناوری نگه می دارد.

ویژگی های XCV200-6FG456C

• دروازه های سیستم: XCV200-6FG456C تقریباً 236،666 دروازه سیستم را ارائه می دهد.این تعداد دروازه بالا امکان اجرای مدارهای منطق یکپارچه پیچیده دیجیتال را بر روی یک تراشه واحد فراهم می کند و باعث افزایش عملکرد و تطبیق پذیری در طیف وسیعی از برنامه ها می شود.

• منابع منطقی: این شامل 1،176 بلوک منطقی قابل تنظیم (CLB) و 5،292 سلول منطقی است.این منابع برای طراحی مدارهای دیجیتال انعطاف پذیر و مقیاس پذیر مناسب هستند.CLB ها را می توان برای انجام طیف گسترده ای از عملکردهای منطقی برنامه ریزی کرد ، در حالی که تعداد زیادی از سلولهای منطقی امکان دستیابی به عملیات و فرآیندهای منطقی گسترده را فراهم می کنند.

• خاطره: این دستگاه 57،344 بیت رم را فراهم می کند که بین بلوک های منطقی آن توزیع شده است.این RAM تعبیه شده برای برنامه هایی که نیاز به ذخیره و بازیابی سریع و کارآمد داده ها دارند ، پشتیبانی می کند و از عملیات داده های پر سرعت در سیستم های دیجیتالی مدرن پشتیبانی می کند.

• قابلیت های I/O: با 284 پین ورودی/خروجی ، XCV200-6FG456C قابلیت های رابط گسترده ای را تسهیل می کند.این پین های I/O از استانداردهای مختلف سیگنال پشتیبانی می کنند و FPGA را قادر می سازد تا به طور مؤثر با سایر اجزای موجود در یک سیستم مانند دستگاه های حافظه ، پردازنده ها و لوازم جانبی ارتباط برقرار کنند.

• ولتاژ و دامنه دما: با ولتاژ اسمی 2.5 ولت ، با دامنه قابل قبول از 2.375 ولت تا 2.625 ولت ، این FPGA ضمن حفظ عملکرد قوی برای مصرف کم مصرف طراحی شده است.این می تواند در محدوده دمای اتصالی از 0 درجه سانتیگراد تا 85 درجه سانتیگراد کار کند و از قابلیت اطمینان در شرایط مختلف محیطی اطمینان حاصل کند.

نمودار عملکرد پین XCV200-6FG456C

در نمودار عملکرد پین XCV200-6FG456C نمایشی ساختاری از تکالیف PIN FPGA است که به بانک های مختلف طبقه بندی می شود (بانک 0 به بانک 7).هر گروه بانکی بر اساس عملکرد و قرار دادن فیزیکی خود در بسته FPGA پین می کند.سیستم شماره گذاری و برچسب زدن از الگوی شبکه ای پیروی می کند که در آن ردیف ها با حروف (A ، B ، C و غیره) و ستون ها بر اساس اعداد (1 ، 2 ، 3 و غیره) مشخص می شوند که شناسایی سریع پین های خاص را تسهیل می کند.این بانک ها با عملکردهای مختلف ورودی/خروجی ، قدرت ، زمین و مسیریابی سیگنال اختصاصی مطابقت دارند.پین ها به گروههای مختلف عملکردی ، از جمله I/O با هدف عمومی (GPIO) اختصاص داده می شوند ، که اغلب به عنوان "G" (ورودی/خروجی عمومی) ، "V" (عرضه ولتاژ) و "O" (خروجی) شناخته می شوند.پین های قدرت و زمین کاملاً مشخص هستند و از عملکرد پایدار FPGA اطمینان می دهند.پین های با هدف خاص مانند ورودی های ساعت ، تنظیم مجدد و سیگنال های کنترل با نمادهایی مانند "R" یا "T." مشخص می شوند.برخی از پین ها همچنین برای برنامه نویسی و اشکال زدایی نقش های ارتباطی اختصاصی ، از جمله پیکربندی JTAG و ساعت با سرعت بالا را ارائه می دهند.

نمودار بلوک XCV200-6FG456C

بلوک ورودی/خروجی

نمودار نمایانگر بلوک ورودی/خروجی (IOB) ساختار XCV200-6FG456C FPGA ، که عضو خانواده Xilinx Virtex است.نمودار عناصر اصلی را که در عملیات ورودی و خروجی نقش دارند ، نشان می دهد و مکانیسم های جریان و کنترل داده را برجسته می کند.در هسته نمودار ، از سه فلیپ فلاپ D برای ثبت سیگنال برای کنترل ورودی ، خروجی و Tri-State استفاده می شود.ثبت خروجی توسط سیگنال OCE (خروجی ساعت فعال) کنترل می شود ، که تعیین می کند چه موقع داده های خروجی بسته می شوند.به طور مشابه ، رجیستری Tri-State توسط TCE (Tri-State Clock Enable) کنترل می شود و بافر خروجی را فعال یا غیرفعال می کند.ثبت ورودی داده های دریافتی را ضبط می کند و قبل از انتقال آن به منطق FPGA داخلی از طریق IBUF (بافر ورودی) ، تأخیر قابل برنامه ریزی را اعمال می کند.Obuft (بافر خروجی Tri-State) تضمین می کند که FPGA می تواند سیگنال را روی پد (پین I/O) سوار کند یا بسته به منطق کنترل ، آن را در حالت آمپسل بالا قرار دهد.برای حفظ آخرین حالت منطقی شناخته شده در هنگام حضور هیچ درایور فعال ، یک مدار نگهدارنده ضعیف روی پد قرار دارد و از شرایط شناور ناخواسته جلوگیری می کند.ولتاژ مرجع (VREF) برای استانداردهای ورودی خاص مانند SSTL یا HSTL استفاده می شود که برای عملکرد مناسب به سطح ولتاژ دقیقی نیاز دارند.به طور کلی ، این ساختار IOB به FPGA اجازه می دهد تا انتقال داده های پر سرعت را مدیریت کند ، از استانداردهای مختلف I/O پشتیبانی کند و کنترل انعطاف پذیر بر زمان سیگنال و یکپارچگی را ارائه دهد.

حالت سریال مستر/برده

در حالت سریال مستر/برده نمودار بلوک فرآیند پیکربندی یک Virtex FPGA ، به طور خاص XCV200-6FG456C را نشان می دهد ، هنگامی که در پیکربندی زنجیره دیزی با استفاده از یک EEPROM سریال (XC1701L) برنامه ریزی می شود.در این تنظیم ، یک دستگاه Virtex به عنوان استاد کار می کند ، کنترل ساعت پیکربندی (CCLK) و انتقال سریال داده های پیکربندی را به FPGA های برده اضافی در زنجیره کنترل می کند.Master FPGA با ادعای سیگنال برنامه ، تنظیم مجدد تمام دستگاه های موجود در زنجیره ، فرآیند پیکربندی را آغاز می کند.پس از اتمام اولیه سازی ، سیگنال INIT نشانگر آمادگی و جریان داده های پیکربندی از سریال EEPROM (XC1701L) به دین (داده در) پین Master FPGA است.Master FPGA داده های EEPROM را می خواند و آن را از طریق DOUT (داده های خارج) به FPGA های برده بعدی منتقل می کند ، و همگام سازی انتقال داده با استفاده از سیگنال CCLK.از سیگنال انجام شده برای نشان دادن پیکربندی موفق استفاده می شود ، با یک مقاومت کشش اختیاری که در هنگام کامل شدن پیکربندی ، حالت بالایی پایدار را تضمین می کند.XC1701L EEPROM توسط Master FPGA با استفاده از CLK ، DATA ، CE (فعال کردن تراشه) و تنظیم مجدد سیگنال های تنظیم مجدد/OE (فعال کردن خروجی) کنترل می شود و اطمینان می دهد که داده های پیکربندی ذخیره شده به درستی بازیابی می شوند.این روش پیکربندی برای برنامه نویسی چندین FPGA با استفاده از یک EEPROM منفرد ، کاهش پیچیدگی سیم کشی خارجی و اطمینان از همه دستگاه ها دریافت داده های پیکربندی هماهنگ است.

مشخصات XCV200-6FG456C

|

نوع |

پارامتر |

|

سازنده |

AMD Xilinx

|

|

سری |

Virtex® |

|

بسته بندی |

سینی |

|

وضعیت جزئی |

منسوخ |

|

تعداد آزمایشگاه ها/CLBS |

1176 |

|

تعداد عناصر/سلول های منطقی |

5292 |

|

کل بیت های قوچ |

57344 |

|

تعداد I/O |

284 |

|

تعداد دروازه ها |

236666 |

|

ولتاژ - عرضه |

2.375V ~ 2.625V |

|

نوع نصب |

سطح سطح |

|

دمای عملیاتی |

0 درجه سانتیگراد 85 درجه سانتیگراد (TJ) |

|

بسته / مورد |

456 BBGA |

|

بسته دستگاه تأمین کننده |

456-fbga (23x23) |

|

شماره محصول پایه |

xcv200 |

برنامه های XCV200-6FG456C

ارتباط از راه دور و شبکه

XCV200-6FG456C به دلیل توانایی آن در انجام انتقال داده های با سرعت بالا و کارهای پیچیده پردازش سیگنال ، در ارتباطات از راه دور و برنامه های شبکه ای برتری دارد.تعداد بالایی از دروازه آن و قابلیت I/O قوی به آن اجازه می دهد تا توابع مانند پردازش بسته ، مدولاسیون سیگنال/تخریب سیگنال و پروتکل های تصحیح خطا را پشتیبانی کند.

پردازش سیگنال دیجیتال (DSP)

ایده آل برای برنامه های DSP ، این FPGA می تواند محاسبات ریاضی سریع و پیچیده مورد نیاز در فن آوری های پردازش صوتی و تصویری را انجام دهد.این که آیا این برای سیستم های چندرسانه ای ، تشخیص صدا و یا سرویس های جریان ، قابلیت پردازش قدرتمند XCV200-6FG456C و پردازش سیگنال با کیفیت بالا و کارآمد است.

سیستم های کنترل صنعتی

در اتوماسیون صنعتی ، XCV200-6FG456C عملکرد لازم را برای مدیریت سیستم های کنترل و شبکه های اتوماسیون فراهم می کند.توانایی آن در انجام چندین کار کنترل به طور همزمان در حالی که تضمین زمان پاسخ باعث می شود آن را برای برنامه های کاربردی در کنترل فرآیند ، روباتیک و دید دستگاه مناسب کند.

سازهای پزشکی

دقت و سرعت FPGA در تجهیزات تصویربرداری پزشکی و تجهیزات تشخیصی بسیار عالی است ، جایی که در پردازش الگوریتم های پیچیده برای تصویربرداری از برنامه های کاربردی مانند MRI ، سونوگرافی و اسکن CT کمک می کند.قابلیت های XCV200-6FG456C اطمینان حاصل می کند که می تواند توان داده های بالا و پردازش پیچیده مورد نیاز در فناوری پزشکی مدرن را کنترل کند.

XCV200-6FG456C قطعات مشابه

مراحل برنامه نویسی XCV200-6FG456C

مراحل برنامه نویسی برای XCV200-6FG456C:

1. ورودی طراحی

مرحله اولیه برنامه نویسی FPGA شامل تعریف منطق دیجیتال و عملکرد سیستم شما است.این کار می تواند با استفاده از زبان های توضیحات سخت افزاری (HDL) مانند VHDL یا Verilog انجام شود ، جایی که شما کدی می نویسید که مشخص می کند چگونه FPGA داده ها را پردازش می کند و با سایر سخت افزار تعامل دارد.از ابزارهای ورودی شماتیک موجود در نرم افزار طراحی FPGA مانند Xilinx ISE یا Vivado می توان استفاده کرد.این روش شامل ایجاد نمای بصری از منطق با کشیدن و رها کردن مؤلفه ها است که برخی از آنها شهودی تر از نوشتن کد هستند.

2. سنتز

پس از اتمام طراحی ، مرحله بعدی سنتز است ، جایی که ابزاری مانند XILINX's XST (فناوری سنتز Xilinx) کد HDL یا طراحی شماتیک شما را به لیست خالص تبدیل می کند.این لیست خالص مدار را از نظر اجزای دیجیتالی عمومی مانند دروازه های منطق و ثبت ها توصیف می کند.فرایند سنتز همچنین شامل بهینه سازی طرح برای برآورده کردن نیازهای عملکرد و به حداقل رساندن مصرف منابع برای عملکرد کارآمد FPGA است.

3. اجرای

فرآیند اجرای با ترجمه آغاز می شود و طراحی شما را با پرونده های محدودیتی ترکیب می کند که پارامترهایی مانند فرکانس ساعت و تکالیف PIN را مشخص می کند.پس از ترجمه ، مرحله نقشه برداری عناصر لیست خالص شما را به منابع فیزیکی خاص در FPGA ، مانند جداول جستجو (LUT) و فلیپ فلاپ ها اختصاص می دهد.مرحله قرار دادن و مسیریابی سپس مکان های فیزیکی هر مؤلفه را در معماری FPGA تعیین می کند و از طریق منابع اتصال قابل برنامه ریزی ارتباط بین آنها برقرار می کند.این مرحله برای دستیابی به معیارهای عملکرد مورد نظر ، از جمله فرکانس های ساعت بسیار عالی است.

4. نسل bitstream

پس از قرارگیری و مسیریابی موفقیت آمیز ، این ابزار یک bitstream ، یک فایل پیکربندی باینری را تولید می کند که شامل تمام اطلاعات برنامه نویسی برای FPGA است.اغلب توصیه می شود که طراحی نهایی پس از قرار دادن طراحی را شبیه سازی کنید تا اطمینان حاصل شود که Bitstream طبق شرایط انتظار می رود.این مرحله تأیید به جلوگیری از مشکلات احتمالی در حین کار واقعی کمک می کند.

5- پیکربندی

مرحله آخر شامل بارگذاری بیت استریم در FPGA با استفاده از روش های مختلف پیکربندی است.حالت Slave-Serial ، یک گزینه ساده و مقرون به صرفه ، FPGA را از طریق یک دستگاه اصلی خارجی که داده های سریال را ارسال می کند ، پیکربندی می کند.در حالت کارشناسی ارشد ، FPGA به طور خودمختار Bitstream را از یک نمایش سریال پیوست می خواند.برای تنظیمات پر سرعت ، SelectMap Mode به یک ریز پردازنده خارجی اجازه می دهد تا داده ها را به سرعت در FPGA بارگیری کند.علاوه بر این ، از حالت JTAG نه تنها برای برنامه نویسی بلکه برای آزمایش و اشکال زدایی نیز استفاده می شود ، با استفاده از یک رابط استاندارد برای برنامه نویسی در سیستم و آزمایش اسکن مرز.

مزایای XCV200-6FG456C

عمل

سری Xilinx Virtex ، که XCV200-6FG456C به آن تعلق دارد ، برای عملکرد پر سرعت بهینه شده است و نرخ ساعت سیستم حداکثر 200 مگاهرتز را ارائه می دهد.این امر باعث می شود تا برنامه هایی که نیاز به پردازش سریع داده ها دارند ، اطمینان حاصل شود که از کارآمد الگوریتم های پیچیده و عملیات پر سرعت مانند ارتباطات ، پردازش و چندرسانه ای استفاده می شود.

پشتیبانی از استانداردهای I/O

این FPGA از طیف گسترده ای از استانداردهای ورودی/خروجی ، از جمله LVTTL ، LVCMOS ، PCI ، GTL ، HSTL ، SSTL ، CTT و AGP پشتیبانی می کند.چنین پشتیبانی گسترده ای از استانداردهای I/O XCV200-6FG456C را قادر می سازد تا یکپارچه با اجزای مختلف سیستم ادغام شود و ابزار خود را در بین اکوسیستم های دیجیتال متنوع تقویت کند.این انعطاف پذیری اجازه می دهد تا FPGA را با شرایط مختلف رابط و بدون اصلاح سیستم تطبیق دهد.

مدیریت ساعت

XCV200-6FG456C دارای چندین حلقه قفل تاخیر (DLL) برای توزیع ساعت و مدیریت در سیستم است.این DLL ها با ارائه سیگنال های ساعت دقیق لازم برای عملیات همزمان ، در بهبود زمان بندی و قابلیت اطمینان سیستم کمک می کنند.این ویژگی در کاهش خطاهای سیستم و تقویت عملکرد کلی ، به ویژه در طرح های پیچیده ای که نیاز به زمان بندی دقیق و هماهنگ سازی دارند ، مهم است.

انعطاف پذیری طراحی

XCV200-6FG456C با داشتن 1،176 بلوک منطق قابل تنظیم و 5،292 سلول منطقی ، منابع منطقی قابل توجهی را با قابلیت اجرای طیف متنوعی از عملکردها ارائه می دهد.از منطق چسب ساده گرفته تا سیستم های دیجیتالی پیچیده ، این FPGA از الزامات طراحی پیچیده پشتیبانی می کند و آن را برای برنامه های کاربردی در محاسبات سفارشی ، پردازش سیگنال دیجیتال و نمونه سازی ایده آل می کند.

نمونه سازی سریع

FPGA هایی مانند XCV200-6FG456C به دلیل توانایی خود در پشتیبانی از نمونه سازی سریع مشهور هستند.این دستگاه امکان تکرار سریع طراحی را فراهم می کند و می تواند در میدان مجدداً تنظیم شود ، که این یک مزیت برای چرخه های توسعه است زیرا باعث کاهش زمان به بازار می شود.همچنین به طور مؤثر با تغییر نیازها یا به روزرسانی ها در مشخصات پروژه سازگار است ، و اطمینان حاصل می کند که محصولات نهایی با آخرین استانداردهای فناوری به روز هستند.

قابلیت ادغام

قابلیت های ادغام XCV200-6FG456C ادغام اجزای چند گسسته را در یک تراشه واحد تسهیل می کند.این ادغام می تواند منجر به کاهش پیچیدگی سیستم ، کاهش مصرف انرژی و صرفه جویی در هزینه شود.این FPGA با به حداقل رساندن تعداد اجزای جداگانه مورد نیاز ، فرآیندهای طراحی را ساده می کند و قابلیت اطمینان و فشردگی سیستم کلی را بهبود می بخشد.

ابعاد بسته بندی XCV200-6FG456C

XCV200-6FG456C یک آرایه دروازه قابل برنامه ریزی در زمینه (FPGA) از سری AMD Virtex® است که در یک بسته آرایه توپ توپ-پچ 456 توپ (FBGA) قرار دارد.

• نوع بسته بندی: 456-fbga

• اندازه بسته بندی: 23 میلی متر x 23 میلی متر

• زمین: 1.0 میلی متر

تولید کننده XCV200-6FG456C

XCV200-6FG456C یک آرایه دروازه قابل برنامه ریزی در زمینه (FPGA) است که در ابتدا توسط Xilinx ساخته شده است ، شرکتی که به دلیل دستگاه های منطقی قابل برنامه ریزی با کارایی بالا شناخته می شود.به دنبال کسب Xilinx توسط amd، XCV200-6FG456C اکنون به عنوان تولید کننده فعلی آن با AMD همراه است.با این حال ، این مدل FPGA منسوخ شده و دیگر در تولید نیست.AMD همچنان به حمایت از معماری های جدیدتر FPGA با عملکرد پیشرفته ، راندمان انرژی و طول عمر طولانی ادامه می دهد و گزینه های مدرن را برای طرح های جدید ارجح می دهد.

پایان

XCV200-6FG456C یک FPGA همه کاره و پر سرعت است که برای بسیاری از برنامه های فناوری مفید است.در حالی که دیگر ساخته نشده است ، اما هنوز هم برای سیستم های قدیمی که نیاز به عملکرد قابل اعتماد دارند ، انتخاب خوبی است.این راهنما طراحی ، مراحل برنامه نویسی و کاربردهای عملی خود را پوشش داده است ، و درک نحوه عملکرد آن و نحوه استفاده از آن را آسان تر می کند.با در دسترس بودن FPGA های جدیدتر ، می توانید از این دانش برای انتخاب FPGA مناسب برای نیازهای خود و بهبود طرح های دیجیتال استفاده کنید.

برگه داده PDF

برگه های XCV200-6FG456C:

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

سوالات متداول [FAQ]

1. مصرف برق XCV200-6FG456C چیست؟

XCV200-6FG456C در 2.5 ولت کار می کند ، با دامنه ولتاژ 2.375 ولت تا 2.625 ولت.مصرف برق به استفاده از منطق و فرکانس ساعت بستگی دارد ، اما به عنوان یک FPGA قدیمی تر ، ممکن است نسبت به دستگاه های Xilinx جدیدتر از قدرت کمتری برخوردار باشد.مدیریت انرژی مناسب و اتلاف گرما باید در نظر گرفته شود.

2. چگونه XCV200-6FG456C با XCV200-6FG256C مقایسه می شود؟

XCV200-6FG456C دارای یک بسته بزرگتر (456-توپ FBGA) در مقایسه با XCV200-6FG256C (256 توپ FBGA) است ، و پین های I/O بیشتری را ارائه می دهد (284 در مقابل 172) و عملکرد بالقوه بهتر برای برنامه های کاربردی که نیاز به واسط گسترده دارند.اگر طراحی شما به قابلیت های بیشتر I/O متکی است ، XCV200-6FG456C انتخاب بهتری است.

3. آیا می توانم چندین بار XCV200-6FG456C را دوباره برنامه ریزی کنم؟

بله ، XCV200-6FG456C یک FPGA مبتنی بر SRAM است ، به این معنی که می توان تعداد نامحدودی از زمان را تا زمانی که برق تأمین شود ، مجدداً برنامه ریزی شود.با این حال ، برای حفظ بیت استریم پس از چرخه برق ، به حافظه غیر فرار خارجی (EEPROM یا FLASH) نیاز خواهید داشت.

4. آیا XCV200-6FG456C از ارتباط سریال پر سرعت پشتیبانی می کند؟

XCV200-6FG456C از چندین استاندارد I/O مانند LVTTL ، LVCMOS ، PCI ، GTL ، HSTL و SSTL پشتیبانی می کند ، اما دارای سرودهای با سرعت بالا (سریال کننده/deserializer) یا فرستنده مانند FPGA های مدرن نیست.برای برنامه هایی که به لینک های سریال با سرعت بالا (به عنوان مثال ، PCIE ، Gigabit Ethernet یا HDMI) نیاز دارند ، مدلهای FPGA جدیدتری را در نظر بگیرید.

5. چگونه XCV200-6FG456C با مدل های FPGA جدیدتر مقایسه می شود؟

XCV200-6FG456C متعلق به نسل قدیمی FPGA است.در مقایسه با Virtex FPGAS مدرن ، دارای تعداد دروازه پایین تر ، سرعت ساعت کندتر و راندمان انرژی محدود است.مدل های جدیدتر چگالی منطق بالاتری ، حافظه تعبیه شده بیشتر ، بلوک های پیشرفته DSP و مصرف انرژی پایین تر را ارائه می دهند و آنها را برای کاربردهای مدرن بهتر می کند.

Pinout ، ویژگی ها و جزئیات فنی AD73322AR توضیح داده شده است

در 2025/03/21

FPGA EP20K100EFC324-1X: ویژگی ها ، مشخصات ، برنامه ها و راهنمای برنامه نویسی

در 2025/03/20

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147778

-

pinout uSB-C و ویژگی های

در 2000/04/18 112029

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111351

-

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83780

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79579

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66971

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63107

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63041

-

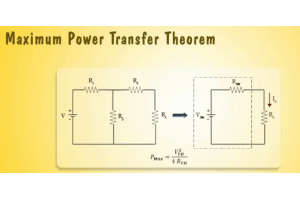

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54097

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52191