درک قدرت قفل S-R: دروازه ای برای الکترونیک مدرن

قفل ها دستگاه های دیجیتالی ساده ای هستند که یک بیت اطلاعات را ذخیره می کنند و آن مقدار را تا زمانی که سیگنال های ورودی جدید دریافت کنند ، نگه می دارند.آنها در سیستم های دیجیتال برای نگه داشتن موقت داده های باینری استفاده می شوند.قفل ها را می توان با استفاده از انواع مختلفی از دروازه های منطق اساسی مانند و ، یا ، نه ، NAND و نه دروازه ها انجام داد.در این مقاله به بررسی طراحی ، عملکرد ، تغییرات و کاربردهای Latch S-R می پردازد ، با تأکید بر بهترین نقش آن در الکترونیک مدرن و استفاده از آن در مدارهای عملی و شبیه سازی های منطق دیجیتال.

کاتالوگ

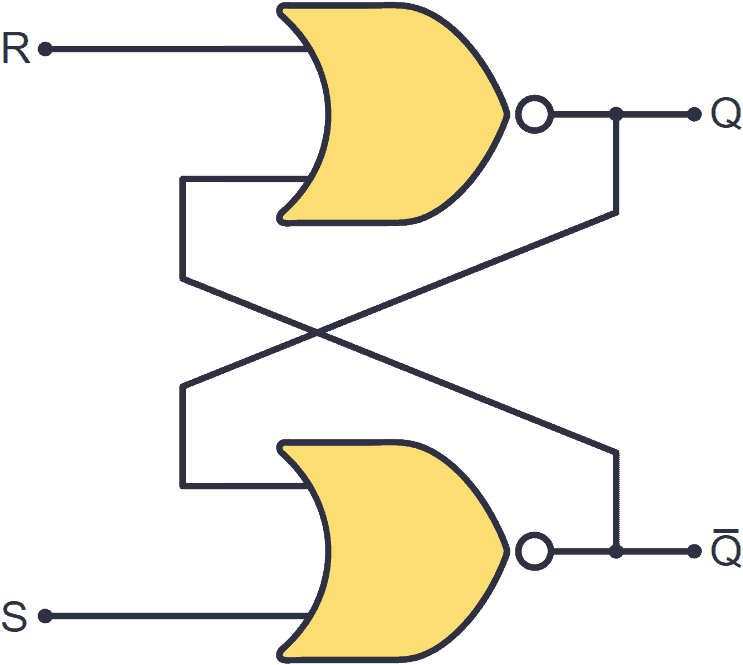

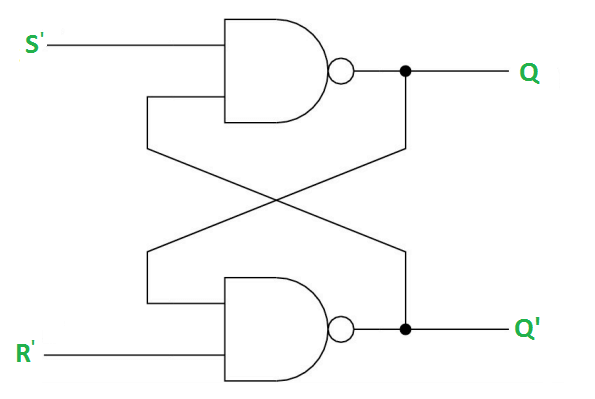

شکل 1: نمودار مدار قفل S-R

ساختار قفل S-R

قفل S-R (Reset) ، سنگ بنای الکترونیک دیجیتال ، یک مولتی وبراتور قابل استفاده است.قادر به حفظ یکی از دو حالت متمایز و پایدار به طور نامحدود و بدون ورودی خارجی است.این عملکرد باعث می شود SR یک مؤلفه اصلی در ذخیره سازی حافظه و تعویض عملیات در دستگاه های الکترونیکی مختلف باشد.

از نظر ساختاری ، قفل SR از دو دروازه به هم پیوسته و نه در یک طرح حلقه بازخورد تشکیل شده است.این ترتیب خاص از آنجا که پیش نیازهای قابل استفاده را ارائه می دهد ، اهمیت دارد.خروجی هر دروازه NOR به طور مستقیم به ورودی دیگری متصل می شود و یک حلقه مداوم از بازخورد ایجاد می کند که زیربنای عملکرد قفل است.

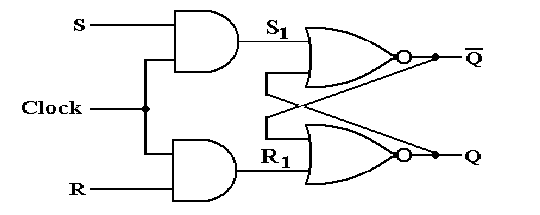

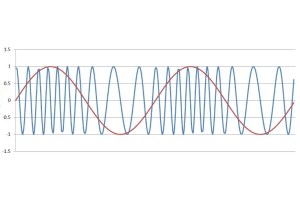

شکل 2: قفل S-R و سیگنال ساعت (CLK)

با گسترش در طراحی اصلی ، قفل SR Gated یک ورودی اضافی ، ورودی: سیگنال ساعت (CLK) را معرفی می کند.این پیشرفت شامل یک ورودی ساعت است که لایه ای از کنترل را به ارمغان می آورد و عملیات قفل را در سیستم هایی که نیاز به همگام سازی دارند ، ادغام می کند.این هماهنگ سازی موظف است که لحظات دقیقی را تعیین می کند که قفل می تواند حالت ها را تغییر دهد ، که به طور مناسب با اصطلاح "دروازه" توصیف شده است.گنجاندن سیگنال ساعت تضمین می کند که تغییر در حالت خروجی قفل فقط در مرحله ساعت فعال رخ می دهد ، به طور معمول در لبه بالا یا در حال سقوط سیگنال CLK.

معرفی ورودی CLK نه تنها خواص قفل اساسی SR را حفظ می کند بلکه عملکرد آن را با پویایی زمانی سیستم های دیجیتال بزرگتر هماهنگ می کند.این تمایل تراز برای حفظ یکپارچگی داده ها و اطمینان از وقوع انتقال حالت بدون اشکال یا تغییرات ناخواسته ، به ویژه در تنظیمات مدار پیچیده که در آن ممکن است چندین بسته باشد.با کنترل هنگامی که قفل به دستورات تنظیم و تنظیم مجدد پاسخ می دهد ، سیستم می تواند از مسائلی مانند شرایط مسابقه و سایر خطاهای مرتبط با زمان جلوگیری کند که در غیر این صورت ممکن است ثبات و عملکرد سیستم را مختل کند.

حالتهای عملیاتی قفل S-R

عملکرد آن به ورودی های دو سیگنال کنترل بستگی دارد: تنظیم (ها) و تنظیم مجدد (R).در اینجا ، ما توضیح می دهیم که چگونه این ورودی ها بر روی خروجی ها و حالت های قفل SR تأثیر می گذارند.

مورد 1: وضعیت تعیین شده

هنگامی که ورودی (S) زیاد است (1) و ورودی تنظیم مجدد (R) کم است (0) ، قفل وارد شرایط تنظیم می شود.در این حالت ، دروازه NAND متصل به ورودی R به دلیل ورودی زیاد از S. سیگنال کم را خروجی می کند.به پایین (0).این حالت پایدار است و تا زمانی که ورودی ها تغییر کند ، Q را بالا نگه می دارد و توانایی قفل در ذخیره وضعیت بالا را نشان می دهد.

شکل 3: حالت تعیین شده

مورد 2: وضعیت تنظیم مجدد

هنگامی که S کم است (0) و R زیاد است (1) ، قفل وارد شرایط تنظیم مجدد می شود.در اینجا ، ورودی بالا در R و ورودی کم در S ، دروازه NAND را که به خروجی R متصل است ، یک سیگنال کم تبدیل می کند.این سیگنال کم Q را به پایین (0) و q-bar به بالا (1) تبدیل می کند ، و به طور موثری قفل را تنظیم می کند.این نشان دهنده توانایی چفت برای بازگشت به حالت کم پایدار در Q در هنگام ورودی های مناسب است.

شکل 4: حالت تنظیم مجدد

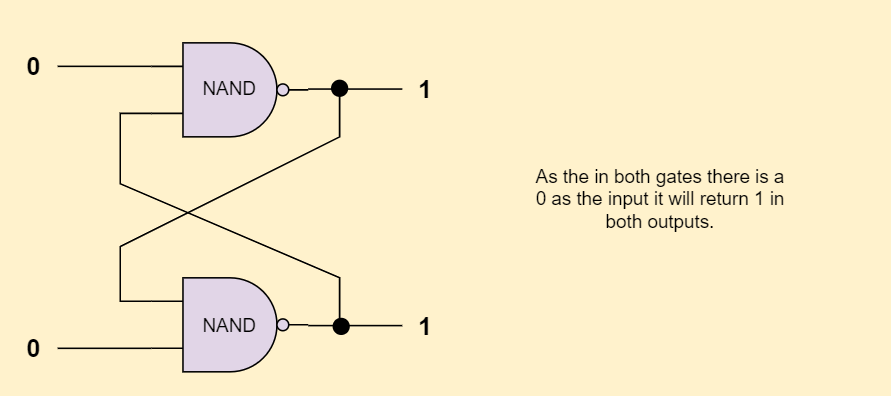

مورد 3: حالت نامعتبر

اگر هر دو S و R کم باشند (0) ، هر دو ورودی به دروازه NAND کم هستند و باعث می شود هر دو خروجی Q و Q-BAR زیاد شوند.این حالت نامعتبر یا ممنوع است زیرا این قانون اساسی را می شکند که Q و Q-BAR همیشه باید مخالف باشند.این سناریو محدودیت Latch SR را برجسته می کند و بر اهمیت اجتناب از چنین حالتهای ناپایدار از طریق مدیریت ورودی مناسب تأکید می کند.

شکل 5: حالت نامعتبر

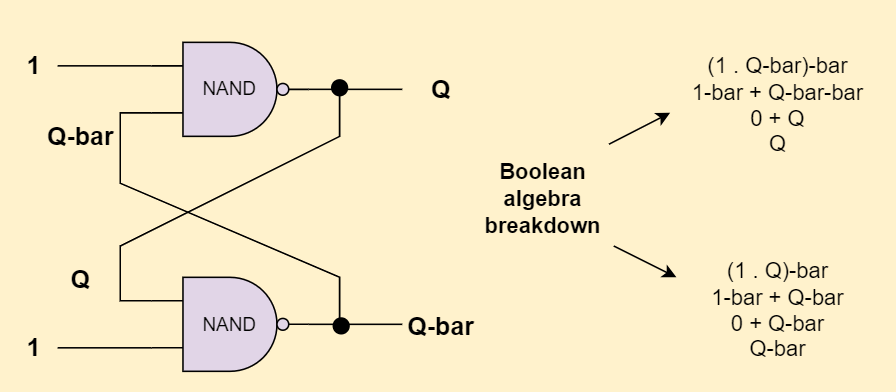

مورد 4: شرایط نگه داشتن

هنگامی که هر دو ورودی زیاد هستند (1) ، خروجی ها به جای ورودی های فعلی به حالت قبلی چت بستگی دارند.این به عنوان شرایط نگهدارنده شناخته می شود ، جایی که Q و Q-BAR بدون تغییر باقی می مانند و آخرین وضعیت معتبر قفل را حفظ می کند.برای برخی از برنامه ها ، این مهم است که بتوانیم حالت قفل شده را برای مدت طولانی و بدون اصلاح ، مانند سلولهای ذخیره سازی حافظه که در آن یکپارچگی داده از اهمیت بالایی برخوردار است ، حفظ کنیم.

شکل 6: حالت نگهدارنده

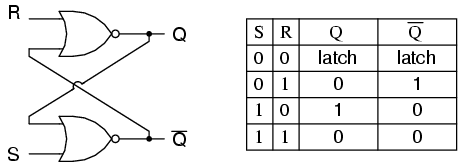

قفل S-R با یک جدول حقیقت

این جدول فقط یک ابزار نظری نیست بلکه برای طراحان مدار و دانش آموزان نیز عملی است.این به آنها کمک می کند تا ببینند که چگونه قفل تحت شرایط بسیاری رفتار می کند.در زیر ، ما جدول حقیقت جامع را برای SR Latch ارائه می دهیم ، و به دنبال آن توضیحات و بینش های عملی برای هر شرایط.

|

حرف |

حرف |

سعدی |

q-bar |

حالت |

|

0 |

0 |

1 |

1 |

نامعتبر |

|

0 |

1 |

0 |

1 |

بازپا |

|

1 |

0 |

1 |

0 |

تنظیم کردن |

|

1 |

1 |

سعدی |

q-bar |

نگه داشتن |

نمودار 1: SR

جدول حقیقت را قفل کنید

توضیح هر ردیف

شرط تنظیم (S = 1 ، R = 0): این ردیف نشان می دهد که وقتی S زیاد است و R کم است ، q روی بالا (1) و q-bar به پایین (0) تنظیم می شود.این آینه پاسخ مدار به یک دستور SET را نشان می دهد و به طور موثری یک "1" را ذخیره می کند.

وضعیت تنظیم مجدد (S = 0 ، R = 1): در اینجا ، ورودی ها نشان دهنده عملکرد تنظیم مجدد است.در نتیجه ، q به پایین (0) بازنشانی می شود و q-bar روی بالا (1) تنظیم شده است.این حالت ظرفیت قفل برای بازگشت به "0" را نشان می دهد.

شرایط نامعتبر (S = 0 ، R = 0): هر دو خروجی در این شرایط زیاد می شوند ، که به طور کلی از آن جلوگیری می شود زیرا منجر به یکسان بودن هر دو خروجی می شود.این می تواند منجر به بی ثباتی یا رفتار نامشخص در قفل شود ، زیرا این قانون را نقض می کند که Q و Q-BAR همیشه باید مخالف باشند.

شرایط را نگه دارید (S = 1 ، R = 1): در این سناریو ، قفل وضعیت قبلی خود را حفظ می کند و توانایی خود را برای نگه داشتن حالت مجموعه آخر نشان می دهد ، مگر اینکه صریحاً دستور تغییر کند.

بینش و نکات عملی

درک خروجی ها: همیشه به یاد داشته باشید که Q و Q-BAR مکمل ایده آل هستند.هرگونه انحراف از این قانون (همانطور که در شرایط نامعتبر مشاهده می شود) نشانگر یک مشکل یا پیکربندی نادرست است.

اجتناب از وضعیت نامعتبر: ضروری است که طراحان مراقبت کنند تا از وضعیتی که S و R در آن کم هستند ، جلوگیری کنند.اجرای منطق اضافی یا درهم آمیختگی می تواند به جلوگیری از این حالت کمک کند.

با استفاده از شرایط نگهدارنده: شرایط نگه داشتن می تواند به ویژه در برنامه هایی که نیاز به حفظ داده ها به مرور زمان دارند ، مناسب باشد.حفظ یکپارچگی داده ها ممکن است به اطمینان از اطمینان از این که قفل ناخواسته به حالت مجموعه یا تنظیم مجدد وارد نشود بستگی دارد.

تفسیر جدول حقیقت: هنگام طراحی یا اشکال زدایی مدارهای اشکال زدایی ، جدول حقیقت را برای پیش بینی اینکه چگونه تغییرات در ورودی بر خروجی تأثیر می گذارد ، به ویژه در مدارهای پیچیده ای که در آن از چفت های متعدد استفاده می شود ، ارجاع دهید.

پویایی عملکردی قفل S-R

قفل S-R (Set-Reset) فقط در صورتی که ورودی های آن به درستی مدیریت شود ، خوب کار می کند.برای درک نحوه عملکرد آن ، باید بدانید که ترکیبات ورودی متفاوت بر روی خروجی ها ، Q و Q-BAR تأثیر می گذارد (برعکس Q).

شکل 7: قفل S-R

اگر هر دو تنظیم (ها) و تنظیم مجدد (R) به طور همزمان فعال شوند (S = 1 و R = 1) ، قفل به "حالت ممنوعه" می رود ، جایی که هر دو خروجی ، Q و Q-Bar ، 0 هستند.این یک مشکل است زیرا به طور معمول ، q و q-bar باید مخالف باشند.

در شرایط عادی ، برای تنظیم قفل ، شما S (تنظیم S به 1) را فعال می کنید و R را غیرفعال می کنید (R را روی 0 تنظیم کنید).این باعث می شود q بالا برود (1) و Q-bar پایین (0) ، نشان می دهد که قفل می تواند 1. را برای تنظیم مجدد قفل ذخیره کند ، شما R (تنظیم R را به 1) فعال می کنید و S را غیرفعال می کنید (تنظیم S).این باعث می شود q پایین (0) و q-bar بالا برود (1) ، نشان می دهد که قفل می تواند خود را پاک کند و یک 0 را ذخیره کند.

هنگامی که هر دو ورودی غیرفعال می شوند (S = 0 و R = 0) ، قفل آخرین حالت خود را نگه می دارد ، یا تنظیم یا تنظیم مجدد می کند.این برای ذخیره داده ها یا نگه داشتن حالت بدون نیاز به ورودی مداوم مفید است.

شرایط مسابقه می تواند عملکرد Latch S-R را پیچیده کند.این خطاها هنگامی اتفاق می افتد که خروجی ها به شدت به زمان تغییر ورودی متکی هستند و در صورت تغییر ورودی ها تقریباً در همان زمان ، منجر به نتایج غیرقابل پیش بینی می شوند.برای جلوگیری از این کار و اطمینان از کارآیی Latch ، از مکانیسم های تأخیر زمان استفاده می شود.این تأخیرها مطمئن می شوند که یک ورودی بعد از اینکه دیگری برای تثبیت زمان فعال شده است ، فعال می شود.برای استفاده از قفل در مدارهای دیجیتال که در آن زمان دقیق مورد نیاز است ، باید به طور مداوم انجام شود و خروجی های پایدار را حفظ کند.این کار با زمان کنترل شده امکان پذیر است.

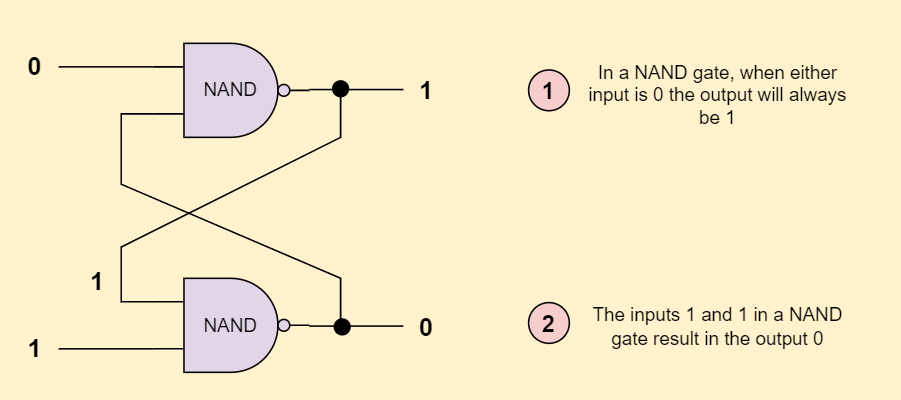

نمودار منطقی قفل S-R

Latch SR یک مدار منطقی منطقی پی در پی با دو تنظیم اصلی است: NOR یا NAND دروازه.هر تنظیم بر نحوه کار و پاسخ دادن به ورودی ها تأثیر می گذارد و امکان سفارشی سازی برای برنامه های الکترونیکی مختلف را فراهم می کند.

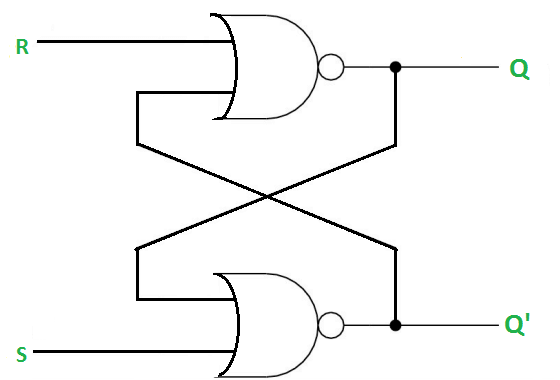

شکل 8: نمودار منطق نشان دهنده قفل S-R با استفاده از دروازه NAND است

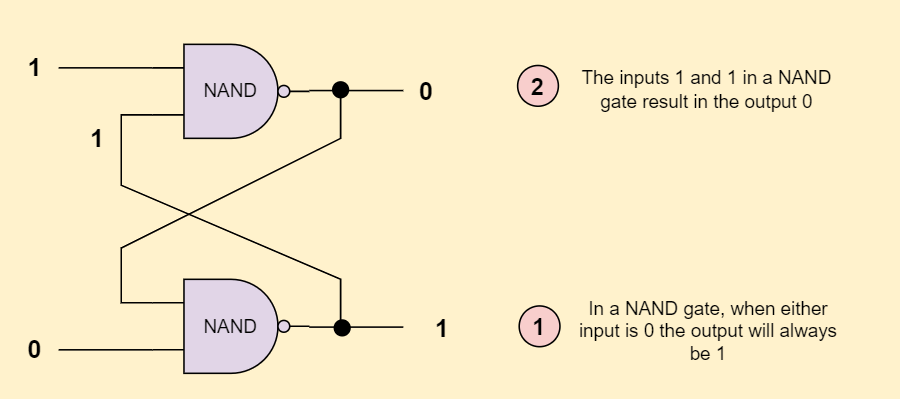

اجرای با استفاده از دروازه های NAND

هنگام ساختن یک قفل SR با دروازه های NAND ، از یک حلقه بازخورد برای حفظ وضعیت خود استفاده می شود.این تنظیم اجازه می دهد تا در صورت کم بودن هر دو ورودی (S و R) ، وضعیت قبلی خود را حفظ کند.NAND Gates Output High مگر اینکه هر دو ورودی زیاد باشند.وضعیت قفل هنگامی که یک ورودی زیاد باشد و دیگری کم باشد تغییر می کند.بهتر است از تنظیم هر دو S و R به طور هم زمان خودداری کنید زیرا این امر هر دو خروجی را مجبور می کند تا پایین بیایند و منجر به حالت نامشخصی شود که در آن خروجی ها دیگر مکمل نیستند.مدیریت صحیح ورودی برای جلوگیری از بی ثباتی در قفل های SR مبتنی بر NAND ضروری است.

اجرای با استفاده از دروازه ها

استفاده از Nor Gates برای یک Latch SR شرایط عملیاتی را در مقایسه با دروازه های NAND تغییر می دهد.در این پیکربندی ، قفل حالت خود را در هنگام بالا بودن هر دو ورودی نگه می دارد.وقتی یک ورودی کم است و دیگری زیاد است ، قفل تغییر می کند.در صورت کم بودن هر دو ورودی ، خروجی و نه دروازه ها زیاد است.این تنظیم در مدارهایی مفید است که حالت پیش فرض این است که هر دو خروجی کم داشته باشند ، و از خروجی قابل پیش بینی در شرایط با ورودی بالا اطمینان حاصل می کنند.با این حال ، بهتر است از تنظیم هر دو ورودی به طور همزمان خودداری کنید ، زیرا این امر باعث خروجی های متناقض می شود و قابلیت اطمینان Latch را کاهش می دهد.

شکل 9: نمودار منطقی نشان دهنده قفل S-R با استفاده از NOR GATE است

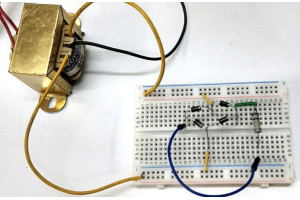

مدار نمونه

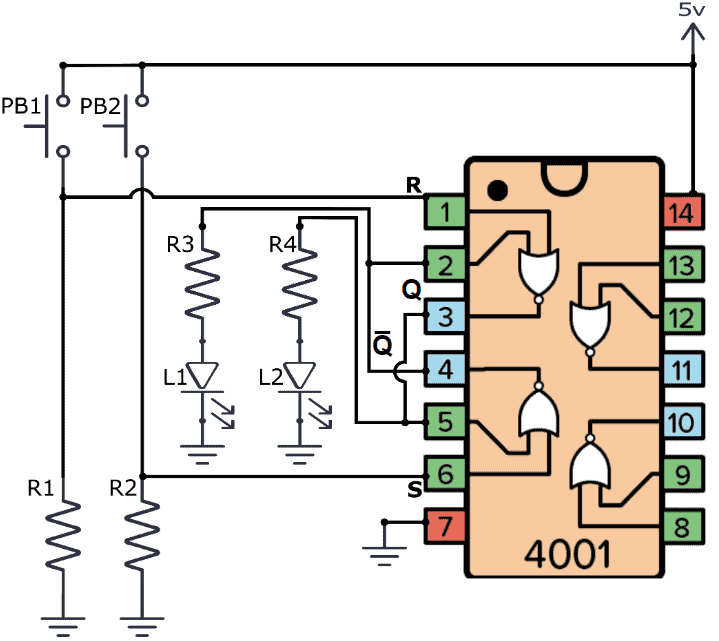

بررسی نحوه عملکرد Latches SR در زندگی واقعی سودمندی آنها را نشان می دهد.مثال خوب یک مدار با استفاده از تراشه CD4001 است که دارای چهار دروازه نیست.این مدار نشان می دهد که چگونه قفل های SR می توانند دستگاه هایی مانند LED را با اقدامات ساده مانند فشار دادن دکمه ها کنترل کنند.

در این مثال ، دروازه های NOR در تراشه CD4001 تنظیم شده اند تا یک قفل SR بسازند.دو دروازه در یک حلقه بازخورد به هم وصل می شوند تا حالت قفل را حفظ کنند.دکمه های فشار به عنوان ورودی برای تنظیم و تنظیم مجدد به مدار اضافه می شوند.با فشار دادن یک دکمه ، وضعیت ورودی را تغییر می دهد ، که قفل و حالت LED را تغییر می دهد.به عنوان مثال ، با فشار دادن دکمه Set LED را روشن می کند ، و حتی پس از انتشار دکمه روشن می شود و نشان می دهد که چگونه قفل می تواند حالت را حفظ کند.

برای بهتر شدن مدار ، LED های بیشتری را می توان اضافه کرد تا وضعیت خروجی Q و Q-BAR را نشان دهد.این امر باعث می شود که نحوه عملکرد قفل ، که در محیط های یادگیری بسیار مفید است ، آسانتر شود.

شکل 10: قفل S-R با استفاده از تراشه CD4001

اجرای کد

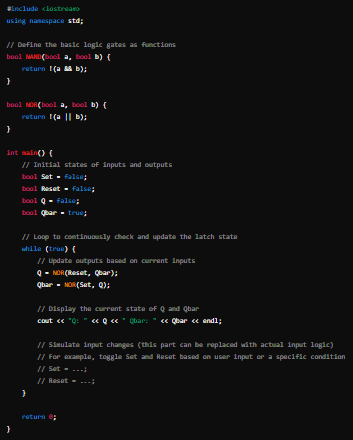

ترجمه منطق عملیاتی یک Latch SR به نرم افزار نشان می دهد که چگونه طراحی منطق دیجیتال می تواند هم در سخت افزار و هم در شبیه سازی های مجازی کار کند.استفاده از یک زبان برنامه نویسی مانند C ++ مؤثر است زیرا از منطق و کنترل پیچیده مورد نیاز برای تقلید از رفتارهای سخت افزاری پشتیبانی می کند.

برای ایجاد یک قفل SR در C ++ ، شما با تعریف دروازه های منطق اساسی به عنوان کارکردهایی که مانند نسخه های سخت افزاری آنها عمل می کنند ، شروع می کنید.به عنوان مثال ، یک عملکرد NAND GATE برعکس و عملکرد را بر روی ورودی های آن باز می گرداند.به همین ترتیب ، یک عملکرد NOR دروازه برعکس عملیات OR را برمی گرداند.با استفاده از این توابع اساسی ، می توانید با ایجاد یک حلقه بازخورد بین این توابع دروازه ، بر اساس نمودار مدار قفل ، رفتار SR Latch را مدل کنید.

این کد به طور معمول دارای حلقه ای است که به طور مداوم حالت های ورودی ها (تنظیم و تنظیم مجدد) را بررسی می کند و بر این اساس خروجی ها (q و q-bar) را به روز می کند.اظهارات مشروط در این حلقه تعیین می کند که چگونه تغییرات در ورودی بر روی خروجی ها تأثیر می گذارد ، و از نزدیک رفتار بدنی SR Latch را تقلید می کند.به عنوان مثال ، اگر هر دو ورودی تنظیم و تنظیم مجدد کم باشند ، خروجی ها یکسان باقی می مانند.اگر مجموعه زیاد باشد و تنظیم مجدد کم باشد ، خروجی q زیاد می شود و Q-BAR کم می شود و وضعیت مجموعه Latch را تکرار می کند.

در اینجا یک مثال ساده از نحوه نگاه این کد در کد آورده شده است:

شکل 11: Latch SR در C ++

این کد یک قفل SR ساده را با استفاده از Nor Gates تنظیم می کند و به طور مداوم حالت قفل را بر اساس ورودی ها بررسی و به روز می کند.

برنامه های Latch SR

سیستم های کنترل در عملیات حرکتی: قفل SR مورد نیاز سیستم برای کنترل موتور.با استفاده از سوئیچ های Pushbutton Start (S) و Stop (R) ، Latch SR حتی پس از انتشار دکمه شروع ، یک موتور را در حال اجرا نگه می دارد.این تنظیم تضمین می کند که موتور به طور مداوم تا زمانی که متوقف شود ، باعث افزایش ایمنی و راحتی می شود.

حافظه و ذخیره سازی داده ها: هنگام ایجاد مدارهای حافظه بزرگتر ، SR Latch نقش دارد زیرا می تواند یک بیت داده را ذخیره کند.این داده ها را در حالت پایدار تا به روزرسانی حفظ می کند و اساس سلولهای حافظه را در محاسبات دیجیتال تشکیل می دهد.

کنترل و مدیریت سیگنال: در برنامه های سیگنال کنترل ، Latches SR بیت های خاص را تا زمان برآورده شدن شرایط خاص نگه می دارد و از توالی و زمان مناسب در عملیات اطمینان می دهد.دقت در پردازش سیگنال و جریان داده به این بستگی دارد.

مدارهای دفع: قفل های SR سیگنال ها را از سوئیچ ها و دکمه های مکانیکی تثبیت می کنند ، و از شروع کار و خطاهای ناشی از "گزاف گویی" هنگام فشار سوئیچ جلوگیری می کنند.این به ویژه در رابط های دیجیتالی مانند صفحه کلید مناسب است.

عناصر اساسی در سیستم های دیجیتال: طراحی فلیپ فلاپ ها و پیشخوان ها ، که برای زمان بندی و توالی در الکترونیک مناسب هستند ، به شدت به قفل های SR متکی است.آنها همچنین به عنوان چفت پالس برای تغییر سریع حالت استفاده می شوند.

برنامه های تخصصی: در سیستم های ناهمزمان ، از تغییراتی مانند D Latch برای انتقال داده ایمن و قابل اعتماد استفاده می شود.در سیستم های دو فاز همزمان ، قفل داده ها باعث کاهش تعداد ترانزیت ، بهبود کارایی و کاهش تأخیر می شود.

پیامدهای گسترده تر در الکترونیک: Latches SR به طور گسترده ای در مدارهای دروازه برق مورد استفاده قرار می گیرد و نقش مهمی در حفظ انرژی در دستگاه های الکترونیکی دارد.آنها حالات قدرت را در سطح مفصلی مدیریت می کنند و به بهره وری کلی انرژی سیستم های دیجیتال کمک می کنند.

پایان

قفل S-R اهمیت ساختارهای منطق ساده را در سیستم های دیجیتالی پیچیده نشان می دهد.با نگاهی به تنظیمات مختلف آن و نحوه عملکرد آن ، می بینیم که قفل S-R داده ها را پایدار نگه می دارد و سیستم ها را کارآمد و قابل اعتماد می کند.این می تواند در شرایط مختلفی کار کند ، که توسط جداول حقیقت و نمودارهای منطقی نشان داده شده است ، و آن را برای چندین کاربرد ، از کنترل موتور گرفته تا مدارهای دیجیتالی اساسی مانند فلیپ فلاپ ها و پیشخوان ها سازگار می کند.قفل S-R در بسیاری از کاربردهای عملی مانند سلولهای حافظه در رایانه ها و مدارهای تزیین شده در رابط های دیجیتال ، افزایش کارایی و کاهش خطاها در دستگاه های الکترونیکی مناسب است.با استفاده از مکانیسم های بازخورد و مدیریت دقیق سیگنال ورودی ، قفل S-R برای طراحی سیستم های دیجیتالی قابل اعتماد تر و کارآمدتر مناسب است.مطالعه عملکرد آن از طریق شبیه سازی نرم افزار به اتصال الکترونیک های نظری با برنامه های دنیای واقعی کمک می کند ، و باعث می شود S-R قفل موضوع مهمی برای هر دو مهندسین الکترونیکی جدید و با تجربه باشد.

سوالات متداول [سؤالات متداول]

1. هدف از Latch SR چیست؟

از Latch SR برای ذخیره یک بیت داده استفاده می شود.این یک شکل اساسی از حافظه در مدارهای دیجیتال است.عملکرد اصلی آن حفظ وضعیت کمی است تا زمانی که توسط سیگنال های ورودی تغییر یابد.

2. آیا SR Latch High یا Low فعال است؟

قفل SR به طور معمول فعال است ، به این معنی که به ورودی های بالا پاسخ می دهد (سطح منطقی 1).هنگامی که ورودی های S (SET) و R (تنظیم مجدد) زیاد هستند ، باعث تغییر در خروجی می شوند.

3. ضرر با قفل SR چیست؟

اشکال اصلی قفل SR حساسیت آن به یک وضعیت نامعتبر است که در آن هر دو ورودی مجموعه و تنظیم مجدد همزمان بالا هستند.این وضعیت منجر به خروجی نامشخص می شود ، که می تواند منجر به رفتار غیرقابل اعتماد یا غیرقابل پیش بینی شود.

4- قوانین مربوط به Latch SR چیست؟

اگر s (set) زیاد باشد و r (تنظیم مجدد) کم باشد ، خروجی q روی بالا تنظیم می شود.

اگر R زیاد باشد و S کم باشد ، خروجی Q به پایین تنظیم می شود.

اگر هر دو S و R کم باشند ، خروجی حالت قبلی خود را حفظ می کند.

اگر هر دو S و R زیاد باشند ، خروجی تعریف نشده یا نامعتبر است.

5- حافظه در SR Latch چیست؟

حافظه در یک قفل SR به توانایی آن در حفظ وضعیت خروجی (بالا یا پایین) به طور نامحدود اشاره دارد ، تا زمانی که ورودی را برای تغییر وضعیت دریافت کند.این باعث می شود آن را به یک دستگاه قابل استفاده ، ایده آل برای ذخیره سازی حافظه ساده تبدیل کند.

6. خروجی های Latch SR چیست؟

Latch SR دارای دو خروجی ، Q و Q '(Q-BAR) است.q وضعیت فعلی را نشان می دهد ، در حالی که q "معکوس Q است. وقتی q زیاد است ، q 'کم است ، و برعکس.

7. از کجا استفاده می کنیم؟

هنگامی که ذخیره داده های کوتاه مدت یا حفظ دولت مورد نیاز است ، لچ ها در انواع مختلف برنامه ها استفاده می شوند.این شامل ذخیره سازی داده ها در Flip-Flops ، ثبت ها و واحدهای حافظه و همچنین در سیستم هایی است که نیاز به همگام سازی داده ها و توابع نگهدارنده مدار دارند.

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

برق استاتیک

در 2024/06/19

ستون فقرات سیستم های برقی: یک راهنمای جامع برای یکسو کننده

در 2024/06/17

پست های محبوب

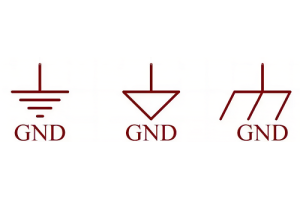

-

GND در مدار چیست؟

در 1970/01/1 2942

-

راهنمای اتصال RJ-45: کدهای رنگی اتصال RJ-45 ، طرح های سیم کشی ، برنامه های R-J45 ، برگه های داده RJ-45

در 1970/01/1 2501

-

انواع اتصال فیبر: SC در مقابل LC و LC در مقابل MTP

در 1970/01/1 2089

-

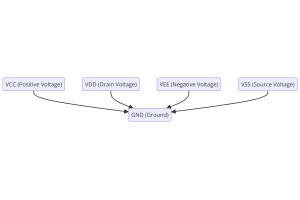

ولتاژ منبع تغذیه در الکترونیک VCC ، VDD ، VEE ، VSS و GND

در 0400/11/9 1895

-

مقایسه بین DB9 و Rs232

در 1970/01/1 1765

-

باتری LR44 چیست؟

برق ، آن نیروی همه گیر ، بی سر و صدا همه جنبه های زندگی روزمره ما را نفوذ می کند ، از وسایل بی اهمیت گرفته تا تجهیزات پزشکی تهدید کننده زندگی ، این نقش خاموش را ایفا می کند.با این حال ، درک این انرژی ، به ویژه نحوه ذخیره و کارآ...در 1970/01/1 1714

-

درک اصول: مقاومت در برابر القاء ، و مقادیر

در رقص پیچیده مهندسی برق ، سه گانه از عناصر اساسی مرحله مرکزی را به خود اختصاص می دهد: القاء ، مقاومت و ظرفیت.هر یک از صفات منحصر به فرد را نشان می دهد که ریتم پویا مدارهای الکترونیکی را دیکته می کند.در اینجا ، ما به سفری برا...در 1970/01/1 1655

-

راهنمای جامع باتری CR2430: مشخصات ، برنامه ها و مقایسه با باتری های CR2032

باتری CR2430 چیست؟مزایای باتری CR2430هنجاربرنامه های باتری CR2430معادل CR2430CR2430 در مقابل CR2032اندازه باتری CR2430هنگام خرید CR2430 و معادل ها به دنبال چه چیزی باشیدبرگه داده PDFسوالات متداول باتری ها قلب دستگاه های الکترونیکی کوچک هستند.د...در 1970/01/1 1555

-

RF چیست و چرا از آن استفاده می کنیم؟

فناوری فرکانس رادیویی (RF) بخش مهمی از ارتباطات بی سیم مدرن است و امکان انتقال داده ها در مسافت های طولانی و بدون اتصالات فیزیکی را فراهم می کند.این مقاله به اصول اولیه RF می پردازد و توضیح می دهد که چگونه تابش الکترومغناطیسی...در 1970/01/1 1541

-

CR2450 در مقابل CR2032: آیا می توان از باتری به جای آن استفاده کرد؟

باتری های منگنز لیتیوم با سایر باتری های لیتیوم شباهت دارند.چگالی انرژی بالا و عمر طولانی مدت ویژگی هایی است که آنها مشترک هستند.این نوع باتری به دلیل ایمنی منحصر به فرد ، اعتماد و نفع بسیاری از مصرف کنندگان را به دست آورد...در 1970/01/1 1512