درک قفل های D در سیستم های دیجیتال

در الکترونیک دیجیتال ، بهبود قطعات مدار برای ثبات و عملکرد بهتر سیستم مورد نیاز است.یک قدم بزرگ حرکت از Latches SR به D Latches است.L Latches ورودی ها را ساده تر و بر روی حالت های تعریف نشده کاهش می دهد و آنها را در طراحی و قابل اعتماد در سیستم های حافظه دیجیتال بهتر می کند.این مقاله به طراحی D Latch ، How It Works و کاربردهای آن می پردازد و اهمیت آن را در مدارهای مدرن برجسته می کند.ما ساختار اصلی آن ، نحوه عملکرد آن و چگونگی قرار گرفتن در سیستم های پیچیده با چند برابر را پوشش خواهیم داد.با بررسی این جنبه ها ، ما می دانیم که چگونه قفل D یکپارچگی داده ها و پیش بینی را در سیستم های دیجیتال بهبود می بخشد و باعث افزایش کارایی و قابلیت اطمینان اجزای الکترونیکی می شود.کاتالوگ

شکل 1: قفل D

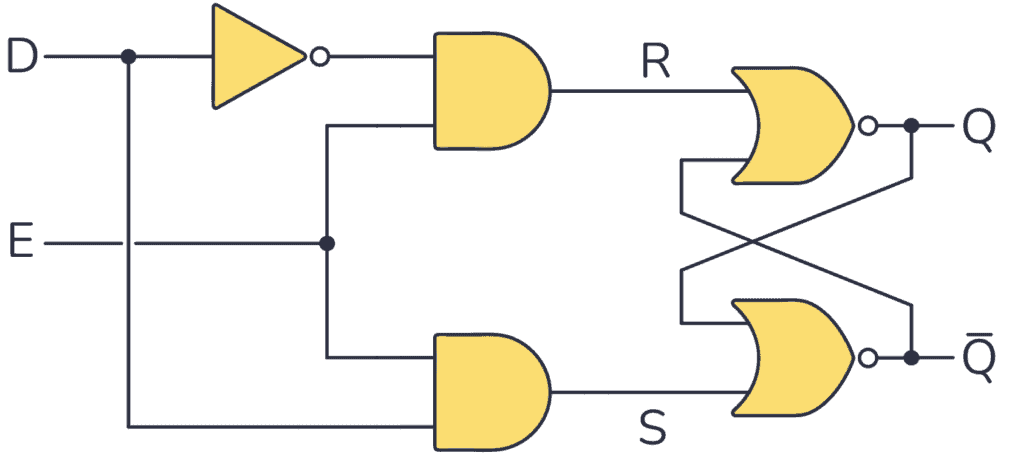

مدارهای قفل D

توسعه مدارهای لچ الکترونیکی تغییرات مهمی را مشاهده کرده است که منجر به ایجاد D Latch می شود ، نسخه بهتری از قفل S-R.در ابتدا ، Latch S-R از ورودی های Set (ها) و تنظیم مجدد (R) استفاده شده است که توسط یک سیگنال فعال برای کنترل در هنگام کار قفل اداره می شود.با این حال ، این طرح های اولیه با کشورهای تعریف نشده مشکل داشتند ، که می تواند باعث شکست سیستم شود.با از بین بردن ورودی تنظیم مجدد و استفاده از ورودی ورودی به عنوان تنها روش کنترل ، فرآیند ورودی بسیار ساده تر شد و سیستم را قابل پیش بینی تر و آسان تر می کند.این تغییر تضمین می کند که خروجی ها ، q و q ، همیشه مخالف بودند و این عملیات را پایدارتر و قابل اطمینان تر می کند.

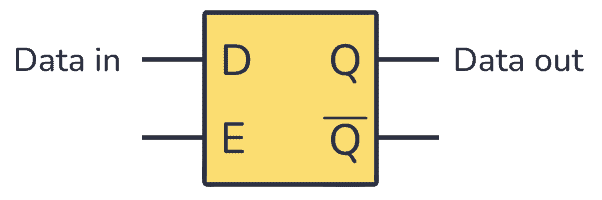

شکل 2: نماد قفل D

ساختار قفل D

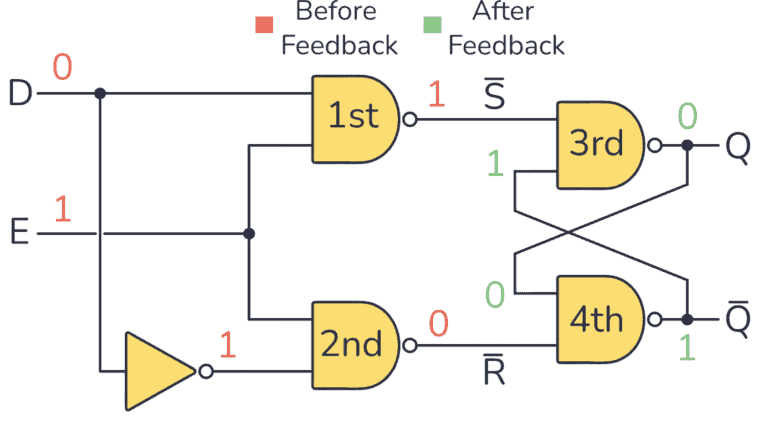

ویژگی اصلی D Latch سیستم تک ورودی آن است که جایگزین طراحی دو ورودی قفل S-R قدیمی تر می شود.این ورودی منفرد ، با نام ورودی داده (D) ، عملکرد قفل را ساده می کند.

در قفل D ، خروجی توسط دو سیگنال کنترل می شود: ورودی داده (D) و سیگنال فعال (E).هنگامی که سیگنال Enable فعال است ، ورودی داده (D) وضعیت خروجی (Q) را تعیین می کند.اگر ورودی داده 1 باشد ، خروجی (q) نیز 1 خواهد بود. اگر ورودی داده 0 باشد ، خروجی (q) 0 خواهد بود. خروجی دیگر ، نه q ، همیشه برعکس Q است. این به معنای این است.که اگر q 1 باشد ، q 0 نخواهد بود و برعکس.

این رابطه بین q و q تضمین می کند که خروجی ها همیشه قابل پیش بینی و پایدار هستند.ساختار D Latch مسائل موجود در Latch S-R قدیمی تر را از بین می برد ، جایی که داشتن دو ورودی گاهی اوقات می تواند به حالتهای تعریف نشده منجر شود.این حالتهای تعریف نشده می تواند باعث نقص مدار شود.

شکل 3: مدار قفل D

قفل های استاندارد D در الکترونیک

قفل D صرفاً یک ایده نظری نیست.این یک بخش واقعی و جدایی ناپذیر است که در بسیاری از الکترونیک یافت می شود.شما می توانید آن را به عنوان یک مؤلفه مدار از پیش بسته بندی شده پیدا کنید ، به این معنی که در هر پروژه ای آماده و آسان است.در شماتیک های الکترونیکی ، قفل D توسط یک نماد استاندارد نشان داده شده است و تشخیص و درک آن را آسان می کند.این نماد استاندارد مهم است زیرا نشان می دهد که چقدر از قفل D در صنعت الکترونیک استفاده می کند.

D Latch به عنوان یک واحد حافظه اساسی در هر نوع سیستم محاسباتی عمل می کند.این به ذخیره و پیگیری داده های باینری کمک می کند ، بهترین کار برای عملکرد مناسب این سیستم ها.از آنجا که قفل D استاندارد است ، تضمین می کند که عملکرد آن در کاربردهای الکترونیکی سازگار است.

شکل 4: قفل D در ذخیره سازی حافظه

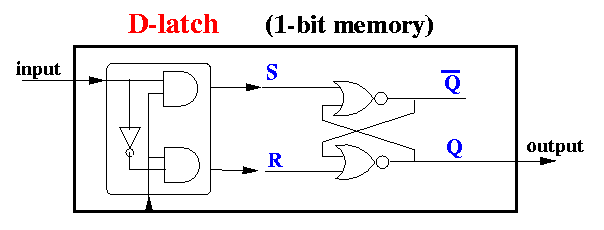

نقش قفل D در سیستم های حافظه دیجیتال

این کار با اجازه ورود داده ها در هنگام بالا بودن یک سیگنال فعال انجام می شود.وقتی این سیگنال زیاد باشد ، هر چیزی که داده می شود توسط قفل D اسیر و نگهداری می شود.به محض اینکه سیگنال Enable به پایین سقوط می کند ، D Latch پذیرش داده های جدید را متوقف می کند و آخرین قطعه داده های دریافت شده را حفظ می کند.و داده ها را پایدار و بدون تغییر نگه می دارد ، حتی اگر بعد از خاموش شدن سیگنال فعال ، در داده های دریافتی تغییراتی ایجاد شود.این ویژگی قفل D برای ذخیره سازی حافظه بسیار مهم است.این بدان معناست که پس از ذخیره داده ها ، ایمن و بدون تغییر باقی می ماند ، که برای یکپارچگی داده ها مناسب است ، به خصوص در سیستم هایی که داده ها باید با گذشت زمان قابل اعتماد و ثابت باشند.توانایی قفل D برای نگه داشتن یک بیت از داده ها به طور قابل اعتماد در شرایط مختلف ، آن را به یک بازیگر اصلی در سیستم های ذخیره سازی حافظه تبدیل می کند.این امر به ویژه در محیط هایی که داده ها باید با دقت حفظ شوند ، مؤثر است.قفل D بسیار سازگار است و آن را در برنامه های دیجیتال ارزشمند می کند.در کنترل کننده های منطق قابل برنامه ریزی ، می تواند جایگزین قفل های S-R در نمودارهای منطق نردبان شود و انعطاف پذیری آن را در محیط های الکترونیکی و محاسباتی نشان می دهد.این تطبیق پذیری تضمین می کند که قفل D در یک فناوری به سرعت در حال تحول مرتبط است.

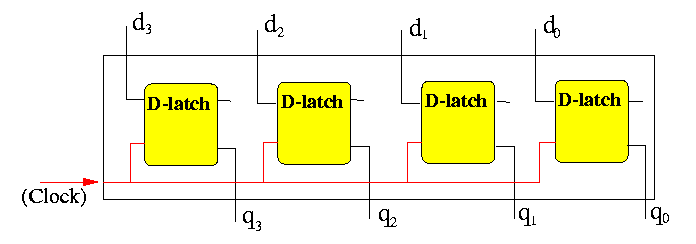

شکل 5: حافظه 4 بیتی با استفاده از چهار قفل D ساخته شده است

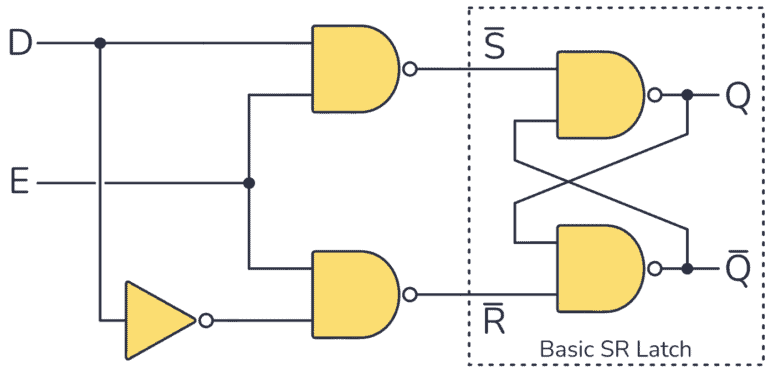

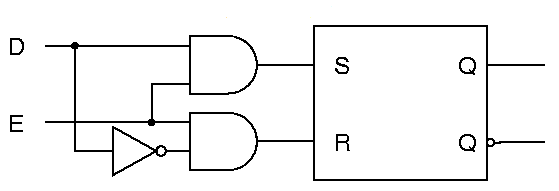

طراحی و تجزیه و تحلیل مدار از قفل D

شکل 6: مدار قفل و دروازه های منطق

D Latch با پرداختن به محدودیت های Latch SR ، پیشرفت مثبتی در طراحی مدار دیجیتال نشان می دهد.این مسئله بر مسئله حالتهای نامعین ایجاد می شود که هر دو ورودی (ها) و تنظیم مجدد (R) در یک قفل SR زیاد هستند.این پیشرفت با ساده کردن طرح ورودی به یک ورودی داده واحد ، معروف به D ، و معرفی اینورتر برای اطمینان از ورودی ها همیشه مکمل حاصل می شود.

این طرح مزایایی را ارائه می دهد.در درجه اول ، این انتقال حالت قابل پیش بینی را بر اساس مقدار ورودی D تضمین می کند.هنگامی که D کم است ، حالت بعدی Latch روی صفر تنظیم می شود.وقتی D زیاد است ، حالت بعدی روی یک تنظیم می شود.این پیش بینی مستقیماً جدول حقیقت SR Latch را نشان می دهد اما با قابلیت اطمینان پیشرفته.D Latch تا زمانی که شرایط فعال سازی برآورده شود ، یکپارچگی داده را حفظ می کند ، و این باعث می شود در مدارهای دیجیتال ، به ویژه در برنامه هایی که نیاز به ذخیره داده های قابل اعتماد مانند دستگاه های حافظه و عناصر ثبت دارند ، خوب باشد.

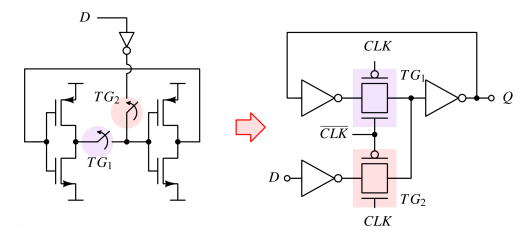

شکل 7: اینورتر پشتی به قفل D Latch

ساخت یک قفل D با استفاده از اجزای دیجیتالی اساسی مانند NAND Gates و Inverters درک ملموس از عملکرد و مزایای آن را فراهم می کند.این رویکرد دستی به ویژه در تنظیمات آموزشی مفید است و به دانش آموزان و علاقه مندان این امکان را می دهد تا رفتار چفت را تحت شرایط مختلف فعال کنند و تجزیه و تحلیل کنند.از طریق آزمایشات عملی ، زبان آموزان بینش عمیق تری در مورد ذخیره حافظه دیجیتال و کنترل سیگنال کسب می کنند.مشاهده چگونگی پاسخ D به بسیاری از ورودی ها و حفظ وضعیت آن ، اهمیت طراحی مدار را در دستیابی به عملکرد دیجیتالی قابل اعتماد تقویت می کند.این آزمایش نیاز به ورودی های مکمل را برای جلوگیری از حالتهای نامشخص ، تحکیم یادگیرنده از اصول طراحی قفل دیجیتال ، برجسته می کند.

مدار قفل D با اضافه کردن دروازه های منطق برای جلوگیری از حالت های نامعتبر و بهبود عملکرد ، قفل SR را تقویت می کند.اینورتر در ورودی D ، همراه با دروازه های NAND ، ورودی فعال (E) را معرفی می کند که هنگام ضبط داده ها کنترل می کند.این تنظیم تضمین می کند که قفل فقط داده ها را از ورودی D به خروجی Q در هنگام فعال بودن سیگنال فعال می کند ، کنترل دقیقی را برای بافر داده ها و برنامه های زمان بندی فراهم می کند.سازگاری مدار بیشتر از طریق تنظیمات بالقوه با استفاده از انواع بسیاری از دروازه ها ، مانند و NOR دروازه ها نشان داده می شود و تطبیق پذیری آن را در سناریوهای منطق دیجیتال نشان می دهد.

شکل 8: اصلاح قفل مبتنی بر اینورتر پشتی به یک قفل D قابل استفاده

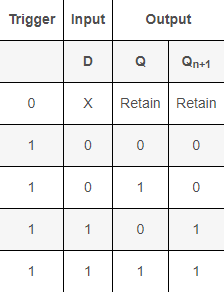

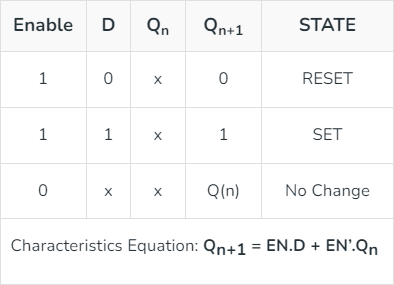

جدول حقیقت Lچچ

درک دستورالعمل های عملیاتی قفل D برای کاربرد آن در مدارهای دیجیتال مورد نیاز است.جدول حقیقت D Latch یک مرور کلی در مورد چگونگی پاسخ قفل به ترکیب های سیگنال ورودی و ساعت ارائه می دهد.این جدول حقیقت ابزاری مناسب برای طراحان است و به آنها امکان می دهد رفتار چفت را در شرایط مختلف پیش بینی کنند و عملکرد مدار را به درستی در برنامه های مورد نظر خود تضمین کنند.

شکل 9: جدول حقیقت D Latch

تجزیه و تحلیل مدار قفل D

تجزیه و تحلیل دقیق از مدار قفل D ، ترتیب استراتژیک دروازه های NAND را نشان می دهد که یکپارچگی سیگنال را حفظ می کند و از درگیری های دولتی جلوگیری می کند.مسیر از ورودی به خروجی با دقت نقشه برداری می شود و نشان می دهد که چگونه هر یک از مؤلفه ها عملکرد قفل را به درستی در شرایط مختلف تضمین می کند.این تفکیک مناسب برای درک چگونگی دستیابی به قابلیت اطمینان مداوم ، با تأکید بر دقت مورد نیاز در طراحی مدار دیجیتال است.

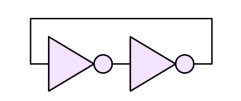

D Latch یک مؤلفه حافظه مورد نیاز در مدارهای دیجیتال است که قادر به حفظ وضعیت فعلی خود یا به روزرسانی آن بر اساس ورودی فعال است.این رفتار در جدول حقیقت D Latch بیان شده است.هنگامی که ورودی Enable کم باشد ، قفل در ورودی D تغییرات را نادیده می گیرد و وضعیت فعلی خود را حفظ می کند.هنگامی که ورودی Enable زیاد باشد ، خروجی Q با ورودی D مطابقت دارد.در سیستم های حافظه دیجیتال و مدارهای منطقی ، ظرفیت D Latch برای نگه داشتن یا به روزرسانی انتخابی ، ثبات داده ها و خروجی های قابل پیش بینی را تضمین می کند.دینامیک زمانبندی D Latch از طریق نمودار زمان بندی آن به بهترین وجه درک می شود ، که نشان می دهد چگونه ورودی و خروجی با سیگنال فعال تعامل دارند.هنگامی که Enable فعال باشد ، خروجی Q ورودی D. را آینه می کند. هنگامی که فعال بودن غیرفعال است ، قفل آخرین حالت خود را حفظ می کند.درک این رفتار D Latch در رابطه با تغییرات در سیگنال فعال ، به ویژه با استفاده از این نمایش گرافیکی می تواند مفید باشد.این بینش ها برای طراحی ، عیب یابی و بهینه سازی مدارهایی که شامل قفل D هستند ، ارزشمند هستند.کاوش در طراحی Latch D از طریق اینورترهای برگشت به عقب ، رویکردهای جایگزین را نشان می دهد که نیازها و محدودیت های خاص طراحی الکترونیکی را برآورده می کند.این روش بر سازگاری D Latch و پتانسیل ابتکاری در راه حل های ذخیره سازی حافظه دیجیتال تأکید دارد.

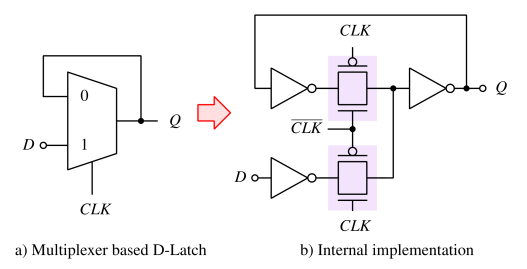

طراحی قفل D مبتنی بر چندگانه

شکل 10: یک قفل D مبتنی بر چند برابر

با استفاده از یک مولتیپلکسر (MUX) ، ساده سازی و سفارشی سازی D Latch D را می توان بدست آورد.یک مولتیپلر بین ورودی های مختلف داده را بر اساس یک سیگنال کنترل انتخاب می کند ، و به D Latch اجازه می دهد تا چندین منبع داده را در همان پیکربندی مدار انجام دهد.این توانایی به ویژه در سیستم های پیچیده ای که ورودی های مختلف داده باید به صورت مشروط پردازش و ذخیره شوند ، مفید است.ادغام یک مولتیپلر با یک قفل D ، با داشتن چندین منبع ورودی ضمن حفظ سادگی در طراحی قفل ، عملکرد را افزایش می دهد.این برنامه در برنامه هایی که نیاز به تعویض سریع بین ورودی های داده های مختلف در شرایط زمان بندی کنترل شده ، مانند سیستم های ارتباطی یا واحدهای محاسباتی پیچیده دارند ، مفید است.استفاده از یک مولتیپلر برای ایجاد یک قفل D ، انعطاف پذیری طراحی قفل را برجسته می کند ، نشان می دهد که چگونه می توان اجزای دیجیتالی استاندارد را برای انجام عملکردهای مشابه از بسیاری جهات تنظیم کرد.این روش درک اصول طراحی منطق دیجیتال و کاربردهای عملی آنها را افزایش می دهد و باعث افزایش تطبیق پذیری در طراحی مدار می شود.

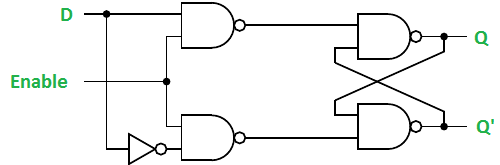

استاندارد قفل های دروازه دار

شکل 11: مدار قفل دروازه D

نمودار منطقی قفل دروازه D

نمودار منطق یک قفل دروازه D ابزاری کلیدی برای ساخت و تجزیه و تحلیل این مدارهای دیجیتال است.این نشان می دهد که چگونه مدار با جزئیات کار می کند ، که برای طراحی یا حفظ سیستم های الکترونیکی دیجیتال مفید است.با نشان دادن هر اتصال و مؤلفه ، نمودار به درک نحوه عملکرد D Latch کمک می کند.

شکل 12: نمودار منطق قفل دروازه D

این نمودار همچنین پیشرفت هایی را در مورد قفل اساسی D نشان می دهد.یکی از پیشرفت های مهم اضافه کردن مکانیسم های کنترل اضافی برای ذخیره بهتر و بازیابی داده ها است.این تغییرات باعث می شود که قفل دروازه D قابل اطمینان تر و کارآمدتر باشد و باعث افزایش عملکرد آن در الکترونیک دیجیتال شود.

پیشرفت ها شامل ویژگی هایی مانند فعال کردن و غیرفعال کردن قفل بر اساس سیگنال های کنترل است که از تغییر داده های ناخواسته در طی عملیات دشوار جلوگیری می کند.این داده ها را در طول عملکرد مدار دقیق نگه می دارد ، که بخشی از سیستم های دیجیتالی پیچیده است که دقت در آن مهم است.نمودار منطق به عنوان راهنمایی برای ساخت یا رفع قفل دروازه D خدمت می کند و به درک بهتر مدارهای دیجیتال کمک می کند.

نقش قفل D در مدارهای دیجیتال

اضافه کردن دروازه به طراحی D Latch ، کنترل در مدارهای دیجیتال را بهبود می بخشد و باعث می شود ذخیره سازی داده ها قابل پیش بینی و پایدارتر باشد.Latch Gated D امکان کنترل داده های به موقع ، تراز کردن ذخیره سازی با مراحل عملیاتی خاص در سیستم های دیجیتال را فراهم می کند.این حق دقیق برای برنامه هایی که نیاز به زمان بندی دقیق و مدیریت سخت دولت در مدارهای دیجیتال پیشرفته دارند.به عنوان یک عنصر اصلی حافظه ، برای مدیریت تغییرات حالت و داده های موجود در مدارهای دیجیتال ، قفل D لازم است.حفظ یکپارچگی و قابلیت اطمینان داده ها نیاز به زمان بندی دقیق و ورودی دقیق داده ها دارد.D Latch داده ها را بر اساس سیگنال های کنترل ضبط و نگه می دارد ، و اطمینان می دهد که به روزرسانی ها فقط در زمان های مناسب اتفاق می افتد ، که از خطا و فساد داده جلوگیری می کند.

جدول حقیقت قفل دروازه D

جدول حقیقت برای قفل دروازه D نتایج خاص را بر اساس شرایط ورودی تشریح می کند.این به عنوان یک راهنمای قطعی برای پیش بینی رفتار چفت در سناریوها ، تقویت طراحی و عملکرد مدارهای دیجیتال که از این مؤلفه استفاده می کنند ، خدمت می کند.

شکل 13: جدول حقیقت قفل دروازه D

پایان

دانستن D Latch نقش خود را در تقویت عملکرد در سیستم های دیجیتال مدرن نشان می دهد.بر خلاف چترهای SR قدیمی تر ، D Latch پیش بینی و ثبات را به ویژه برای فناوری امروز به ارمغان می آورد.سیستم ورودی ساده آن از حالت های نامشخص جلوگیری می کند و داده ها را در شرایط مختلف دست نخورده نگه می دارد.استفاده از مولتیپلکسرها و نسخه های دروازه دار انعطاف پذیری و توسعه مداوم D را برای پاسخگویی به نیازهای پیشرفته فناوری نشان می دهد.استفاده استاندارد آن در هر سیستم عامل اهمیت آن در طراحی مدار دیجیتال را تأیید می کند.این مقاله مزایای فنی D Latch و تأثیر بسیار زیادی در توسعه سیستم حافظه دیجیتال را نشان داده است و این بهترین ابزار برای مهندسان و طراحان در الکترونیک دیجیتال است.

سوالات متداول [سؤالات متداول]

1. قفل D چیست؟

قفل D (قفل داده یا قفل شفاف) یک نوع ساده از مدار فلیپ فلاپ است که در درجه اول برای ذخیره داده های باینری استفاده می شود.این شامل یک ورودی داده ، خروجی و ورودی سیگنال کنترل است که معمولاً به عنوان ورودی یا ورودی ساعت گفته می شود.قسمت اصلی یک قفل D ، گرفتن و نگه داشتن مقدار ورودی باینری است و تا زمانی که سیگنال کنترل اجازه می دهد ، آن را در خروجی در دسترس قرار می دهد.

2. عملکرد قفل دروازه D چیست؟

Latch Gated D به عنوان یک دستگاه ذخیره سازی داده ها عملکردی را انجام می دهد که اجازه می دهد داده ها بر اساس وضعیت سیگنال کنترل آن ذخیره و بازیابی شوند.هنگامی که ورودی فعال (یا ساعت) فعال است ، قفل "به ورودی داده ها" گوش می دهد و آن را به خروجی منتقل می کند.هنگامی که ورودی فعال غیرفعال باشد ، خروجی آخرین مقدار داده را که ورودی بود در حالی که سیگنال فعال فعال بود ، حفظ می کند.

3. قفل D بر اساس کدام دروازه است؟

قفل D به طور معمول مبتنی بر NAND یا NOR GATES است.این دروازه ها به گونه ای پیکربندی شده اند که یک حلقه بازخورد ایجاد می کنند و به دستگاه امکان می دهد حتی پس از تغییر شرایط ورودی ، حالت خروجی (داده های ذخیره شده) خود را حفظ کند.

4- چگونه می توان یک قفل D درست کرد؟

برای ساخت یک قفل d ، شما با تنظیم NAND یا NOT GATES در یک مدار بازخورد شروع می کنید.تنظیم اصلی شامل استفاده از دو دروازه برای ایجاد حلقه ای است که تا زمانی که سیگنال کنترل تغییر کند ، خروجی را حفظ می کند.ورودی داده ها را به یکی از دروازه هایی که خروجی آن تغذیه می کند به یک دروازه دوم متصل کنید ، که به نوبه خود عملکرد دروازه اول را بر اساس شرایط سیگنال فعال کنترل می کند.

5- عملکرد قفل D چیست؟

همانطور که اشاره شد ، عملکرد قفل D ذخیره یک بیت داده و تهیه یک خروجی پایدار تا زمانی که سیگنال کنترل بدون تغییر باقی بماند.این دستگاه به عنوان یک واحد حافظه اساسی در سیستم های الکترونیکی ، اسیر و نگه داشتن داده ها به صورت پویا مطابق نیاز توسط سیستم انجام می شود.

6. چرا Latch Gated D نامیده می شود؟

قفل D Gated D به عنوان یک قفل شفاف خوانده می شود زیرا وقتی سیگنال Enable فعال باشد ، تغییرات در ورودی داده مستقیماً در خروجی منعکس می شود ، سپس قفل را "شفاف" به عبور داده ها می کند.این شفافیت دارای پردازش داده های زمان واقعی است که به روزرسانی های فوری به خروجی مورد نیاز است.

7. چگونه داده های فروشگاه D را ذخیره می کنند؟

D-Latch داده ها را با استفاده از مکانیسم حلقه بازخورد خود ذخیره می کند.هنگامی که سیگنال Enable فعال است ، ورودی داده از طریق دروازه ها تغذیه می شود تا حالت خروجی را تنظیم کند.به محض غیرفعال شدن Enable ، خروجی دروازه ها به ورودی های خود حلقه می شوند و آخرین حالت را به طور نامحدود حفظ می کنند تا زمانی که فعال شود دوباره با داده های جدید فعال شود.این حلقه برگشت خروجی به ورودی همان چیزی است که به D-Latch اجازه می دهد داده ها را بدون تازه کردن خارجی نگه دارد.