راهنمای دانش را تحریک کنید - جوانب مثبت و منفی ، نحوه عملکرد آن ، انواع

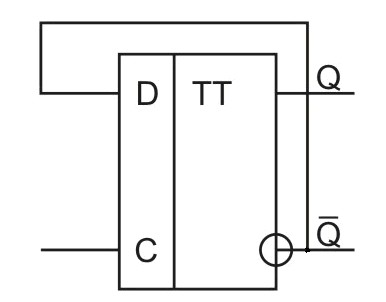

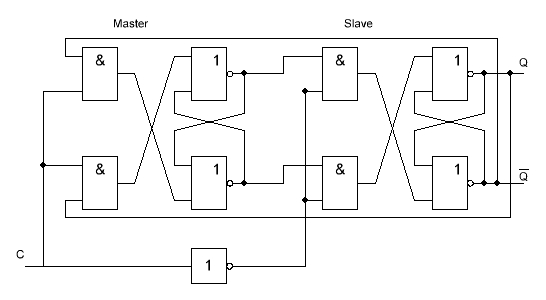

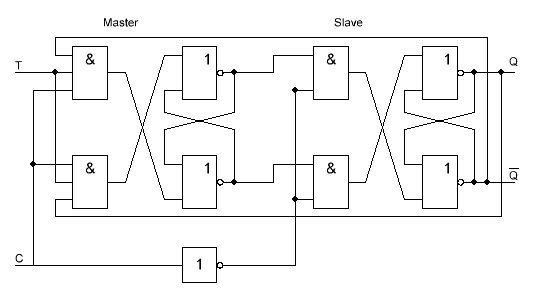

فلفل های t-flip مشابه JK flip-flops هستند.با اتصال ورودی های J و K ، می توان یک فلیپ فلاپ را به دست آورد.مانند یک فلیپ فلاپ ، فقط یک ورودی خارجی به همراه یک ساعت دارد.

کاتالوگ

چگونه t-flip-flops کار می کند

فلاپ های تلنگر ساده ترین دستگاه ها در اتومات های دیجیتال هستند که دارای دو حالت پایدار هستند.یک ایالت دارای مقدار "1" و دیگری "0" استوضعیت دستگاه و اطلاعات باینری ذخیره شده در آن توسط سیگنال های خروجی تعیین می شود: مستقیم و معکوس.اگر یک پتانسیل بر روی خروجی مستقیم مطابق با خروجی منطقی تنظیم شود ، دستگاه در یک حالت تک محرک قرار دارد (پتانسیل خروجی معکوس با صفر منطقی مطابقت دارد).اگر در خروجی مستقیم پتانسیل وجود نداشته باشد ، دستگاه در حالت صفر قرار دارد.

انواع t-flip-flops

فلفل های T-Flip در درجه اول در دو نوع قرار می گیرند:

محرک T-Trigger

T-Trigger

هر دو نوع T-Flip-Flops به طور مشابه کار می کنند.تنها تفاوت در روند انتقال از یک ایالت به حالت دیگر است.نوع ناهمزمان این انتقال را مستقیماً انجام می دهد ، در حالی که نوع همزمان بر اساس این سیگنال کار می کند.

هنگام ارزیابی سناریویی که ورودی ساعت همیشه زیاد باشد (1) ، لازم است دو حالت بالقوه ورودی ضامن (t) ، یا بالا (1) یا کم (0) را در نظر بگیرید.بیایید نتایج مربوط به هر حالت و تعامل دروازه منطق را در آن شرح دهیم.

مورد 1: t = 0

- شرایط خروجی: در اینجا ، هر دو GATE1 و GATE2 و دروازه های متصل به T (تنظیم شده روی 0) هستند.

- خروجی GATE1 و GATE2: از آنجا که And And Gate 0 در حالی که هر یک از ورودی های آن 0 است ، خروجی های 0 ، خروجی های GATE1 و GATE2 همیشه بدون در نظر گرفتن ورودی های دیگر آنها 0 خواهد بود.

- GATE3/Q (N+1) منطق: GATE3 تحت تأثیر خروجی GATE1 قرار دارد.هنگامی که GATE1 از 0 خارج می شود ، معادله منطق GATE3 به ساده (0 یا نه Q) ساده می شود ، و در نتیجه Q.

- GATE4/Q (N+1) منطق: GATE4 از یک الگوی مشابه پیروی می کند ، تولید نمی کند (0 یا Q) ، ساده سازی به عدم Q یا Q '.

خلاصه مورد 1:

- با فرض GATE1 = 0 و GATE2 = 0 ، و استفاده از ویژگی و دروازه ها (هر ورودی 0 منجر به خروجی 0 می شود) ، این عملیات ساده است:

- GATE3/Q (N+1) به عنوان Q محاسبه می شود ، و حالت فعلی را حفظ می کند.

- GATE4/Q (N+1) "منجر به Q" ، مکمل حالت فعلی می شود.

مورد 2: t = 1

- شرط خروجی: هنگامی که T روی 1 تنظیم شده است ، ورودی های GATE1 و GATE2 اکنون خروجی سایر عملیات منطقی را نشان می دهد و بر روی خروجی های آنها تأثیر می گذارد.

- خروجی GATE1 و GATE2: GATE1 مستقیماً به حالت فعلی Q و GATE2 متصل می شود تا Q یا Q نباشد.

- منطق Gate4/Q (n+1): در اینجا ، معادله ساده می شود زیرا ورودی های دروازه و مخالف (q و نه q) هستند ، و در نتیجه 0.

- GATE3/Q (N+1) منطق: از طرف دیگر ، GATE3 با q یا q 'سروکار ندارد ، خروجی نه (q و 0) ، ساده سازی به عدم Q یا Q'.

خلاصه مورد 2:

- تنظیم منطق منجر به تعامل جالب می شود:

- GATE1 = Q ، GATE2 = Q ، ، بر فرآیندهای منطق بعدی تأثیر می گذارد.

- GATE4/Q (N+1) 'مستقیماً به عنوان 0 محاسبه می شود ، زیرا و عملکرد بین q و q نمی تواند درست باشد.

- GATE3/Q (N+1) سپس به عنوان Q 'محاسبه می شود ، که ضامن از حالت قبلی در هنگام T 0 بود.

جدول حقیقت t flip-flop

|

کلوچه |

حرف |

س (n+1) |

حالت |

|

|

0 |

سعدی |

بدون تغییر |

|

|

1 |

س ' |

پیچیدن |

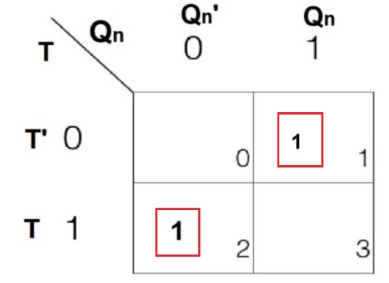

ما از این جدول حقیقت برای تهیه یک جدول مشخصه برای t flip-flop استفاده خواهیم کرد.در جدول حقیقت ، فقط یک ورودی T و یک خروجی Q (N+1) می توانید مشاهده کنید.با این حال ، در جدول مشخصه ، دو ورودی T و QN و یک خروجی Q (N+1) را مشاهده خواهید کرد.

از نمودار منطق بالا ، واضح است که QN و QN 'دو خروجی مکمل هستند ، همچنین به عنوان ورودی برای GATE3 و GATE4 عمل می کنند ، بنابراین ما QN (یعنی وضعیت فعلی Flip-Flop) را به عنوان یک ورودی و Q (در نظر می گیریم (به عنوان مثال ، ما QN (یعنی وضعیت فعلی Flip-Flop) را در نظر می گیریم و Q (n+1) به عنوان خروجی برای حالت بعدی.

پس از تکمیل جدول مشخصه ، ما یک نقشه K 2 متغیر را برای استخراج معادله مشخصه می سازیم.

|

حرف |

qn |

س (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0

|

از نقشه K ، دو جفت به دست می آورید.حل هر دو ، ما معادله مشخصه زیر را دریافت می کنیم:

q (n + 1) = tqn ' + t’qn = t xor qn

مزایای استفاده از t-flip-flops

در مدارهای دیجیتال ، فلاپ های t-flip چندین مزیت مهم ارائه می دهند که عملکرد و ادغام آنها را ساده می کند:

- سادگی ورودی واحد: T-Flip-Flops فقط یک ورودی دارد و عملکرد آنها را ساده می کند.این ورودی واحد می تواند بین حالت های بالا و پایین جابجا شود و به آن اجازه می دهد تا یکپارچه در طرح های مدار ادغام شود و به راحتی با سایر مدارهای دیجیتال ارتباط برقرار کند.

- هیچ ایالات نامعتبر: فلاپ های T-Flip فاقد حالت های نامعتبر هستند و به جلوگیری از رفتارهای غیرقابل پیش بینی در سیستم های دیجیتال کمک می کنند.این قابلیت اطمینان برای حفظ عملکرد سیستم سازگار بسیار مهم است.

- کاهش مصرف برق: در مقایسه با سایر فلیپ فلاپ ها ، T-Flip-Flops قدرت کمتری مصرف می کنند.این راندمان انرژی برای افزایش عمر باتری دستگاه های قابل حمل و کاهش هزینه های انرژی سیستم های دیجیتالی بزرگ مفید است.

- عملیات قابل استفاده: مانند سایر فلیپ فلاپ ها ، T-Flip-Flops دارای عملکرد قابل استفاده است ، به این معنی که آنها می توانند به طور نامحدود حالت (0 یا 1) را نگه دارند تا اینکه توسط یک سیگنال ورودی ایجاد شود.این ویژگی برای برنامه هایی که نیاز به ذخیره طولانی مدت داده های تک بیتی دارند ، ضروری است.

- اجرای آسان: T-Flip-Flops را می توان به راحتی با استفاده از دروازه های منطق اساسی اجرا کرد.این سادگی آنها را برای بسیاری از سیستم های دیجیتال به یک انتخاب اقتصادی مناسب تبدیل می کند و به کاهش هزینه های کلی سیستم کمک می کند.

محدودیت های T-flip-flops

با وجود این مزایا ، FLIP-FLOPS همچنین محدودیت هایی دارند که ممکن است بر مناسب بودن آنها برای برخی از برنامه های کاربردی تأثیر بگذارد:

- خروجی معکوس: خروجی T-Flip-Flops برعکس ورودی آن است که می تواند طراحی مدارهای منطق زمان بندی را پیچیده تر کرده و طراحی را پیچیده تر کند.طراحان برای اطمینان از رفتار صحیح مدار باید این موضوع را در نظر بگیرند.

- عملکرد محدود: T-Flip-Flops فقط می تواند یک بیت اطلاعات را ذخیره کند و قادر به انجام عملیات پیچیده مانند افزودن یا ضرب نیستند و استفاده از آنها را در کارهای اصلی حافظه محدود می کنند.

- حساسیت به اشکالات: فلوپ های t-flip ممکن است به اشکالات و نویز در سیگنال ورودی حساس باشند ، که به طور بالقوه باعث ایجاد تغییرات حالت غیر منتظره می شود.این حساسیت می تواند منجر به رفتار غیرقابل پیش بینی در سیستم های دیجیتال ، به ویژه در محیط هایی با تداخل الکترونیکی بالا شود.

- تأخیر انتشار: مانند همه فلیپ فلاپ ها ، T-Flip-Flops با تأخیرهای انتشار روبرو می شوند ، که ممکن است مسائل مربوط به زمان بندی را در سیستم هایی با محدودیت زمان بندی دقیق معرفی کند.این تأخیرها باید در طول طراحی سیستم در نظر گرفته شود تا از خطاهای زمان بندی جلوگیری شود و از عملکرد قابل اعتماد اطمینان حاصل شود.

برنامه

فلفل های T-Flip در برنامه های مختلف در دنیای واقعی استفاده می شوند از جمله:

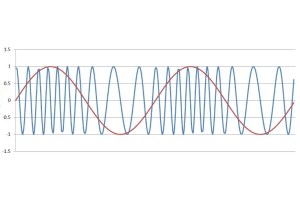

- تقسیم فرکانس: T-Flip-Flops اغلب برای نصف فرکانس یک سیگنال ساعت استفاده می شود.آنها با جابجایی وضعیت فلیپ فلاپ با هر پالس ساعت ، آنها به طور مؤثر فرکانس سیگنال ورودی را به دو تقسیم می کنند و آنها را برای زمان بندی دقیق و ساعتهای دیجیتال و سینت سایزرهای فرکانس ایده آل می کنند.

- دو برابر کردن فرکانس: در مقابل ، Flip-Flops همچنین می تواند برای دو برابر کردن فرکانس یک سیگنال ساعت ، معروف به دو برابر شدن فرکانس استفاده شود.این با پیکربندی فلیپ فلاپ ها در یک مجموعه که فرکانس خروجی را دو برابر سیگنال ورودی ایجاد می کند ، حاصل می شود.

- ذخیره داده ها: T-Flip-Flops می تواند به عنوان بلوک های اصلی ساختمانی برای ذخیره بیت های داده منفرد استفاده شود ، جایی که داده ها برای پردازش یا انتقال بیشتر باید به طور موقت ذخیره شوند.این امر باعث می شود آنها در برنامه هایی مانند رجیسترهای شیفت و دستگاه های ذخیره سازی بسیار مفید باشند.

- پیشخوان ها: یکی دیگر از کاربردهای مهم T-flip-flops ایجاد پیشخوان های باینری است.آنها می توانند با سایر دروازه های منطق دیجیتال به هم پیوسته باشند تا پیشخوان هایی را بسازند که بر اساس نیازهای طراحی می توانند شمارش را افزایش دهند یا کاهش دهند.

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

→ قبلی

درک ظرفیت باتری خودرو و نحوه عملکرد آن در شرایط مختلف برای هر صاحب ماشین مهم است ، به خصوص هنگامی که با چالش های شدید آب و هوایی روبرو شوید.رتبه آمپر میل لنگ (CCA) یک اقدا...

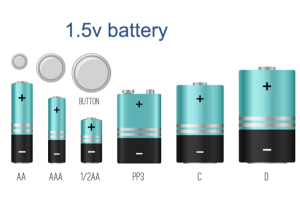

کاوش در پویایی باتری های 1.5 ولت نه تنها نقش مهم آنها را در نیرو دادن به مجموعه متنوعی از دستگاه ها بلکه همچنین زمینه های غنی تاریخی و فناوری آنها نشان می دهد.این باتری ...

→ بعد

چقدر در مورد CCA می دانید؟

در 2024/04/26

باتری 1.5 ولت - چقدر می دانید؟

در 2024/04/25

پست های محبوب

-

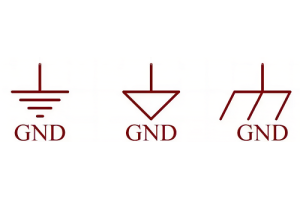

GND در مدار چیست؟

در 1970/01/1 2942

-

راهنمای اتصال RJ-45: کدهای رنگی اتصال RJ-45 ، طرح های سیم کشی ، برنامه های R-J45 ، برگه های داده RJ-45

در 1970/01/1 2501

-

انواع اتصال فیبر: SC در مقابل LC و LC در مقابل MTP

در 1970/01/1 2089

-

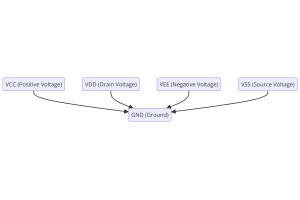

ولتاژ منبع تغذیه در الکترونیک VCC ، VDD ، VEE ، VSS و GND

در 0400/11/9 1895

-

مقایسه بین DB9 و Rs232

در 1970/01/1 1765

-

باتری LR44 چیست؟

برق ، آن نیروی همه گیر ، بی سر و صدا همه جنبه های زندگی روزمره ما را نفوذ می کند ، از وسایل بی اهمیت گرفته تا تجهیزات پزشکی تهدید کننده زندگی ، این نقش خاموش را ایفا می کند.با این حال ، درک این انرژی ، به ویژه نحوه ذخیره و کارآ...در 1970/01/1 1714

-

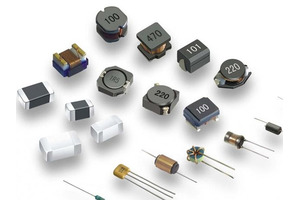

درک اصول: مقاومت در برابر القاء ، و مقادیر

در رقص پیچیده مهندسی برق ، سه گانه از عناصر اساسی مرحله مرکزی را به خود اختصاص می دهد: القاء ، مقاومت و ظرفیت.هر یک از صفات منحصر به فرد را نشان می دهد که ریتم پویا مدارهای الکترونیکی را دیکته می کند.در اینجا ، ما به سفری برا...در 1970/01/1 1655

-

راهنمای جامع باتری CR2430: مشخصات ، برنامه ها و مقایسه با باتری های CR2032

باتری CR2430 چیست؟مزایای باتری CR2430هنجاربرنامه های باتری CR2430معادل CR2430CR2430 در مقابل CR2032اندازه باتری CR2430هنگام خرید CR2430 و معادل ها به دنبال چه چیزی باشیدبرگه داده PDFسوالات متداول باتری ها قلب دستگاه های الکترونیکی کوچک هستند.د...در 1970/01/1 1555

-

RF چیست و چرا از آن استفاده می کنیم؟

فناوری فرکانس رادیویی (RF) بخش مهمی از ارتباطات بی سیم مدرن است و امکان انتقال داده ها در مسافت های طولانی و بدون اتصالات فیزیکی را فراهم می کند.این مقاله به اصول اولیه RF می پردازد و توضیح می دهد که چگونه تابش الکترومغناطیسی...در 1970/01/1 1541

-

CR2450 در مقابل CR2032: آیا می توان از باتری به جای آن استفاده کرد؟

باتری های منگنز لیتیوم با سایر باتری های لیتیوم شباهت دارند.چگالی انرژی بالا و عمر طولانی مدت ویژگی هایی است که آنها مشترک هستند.این نوع باتری به دلیل ایمنی منحصر به فرد ، اعتماد و نفع بسیاری از مصرف کنندگان را به دست آورد...در 1970/01/1 1512