درک d flip-flops: کار ، برنامه ها و مزایا

این راهنما توضیح می دهد که یک flip-flop چیست و چگونه در مدارهای دیجیتال کار می کند.شما همچنین در مورد چفت های 4 بیتی و 8 بیتی ، نحوه کار آنها با هم و از کجا استفاده می شود.این راهنما شامل نمونه هایی از نحوه استفاده از F Flip-Flops در رایانه ها ، تایمرها ، سیستم های ارتباطی و دستگاه های تعبیه شده است.همچنین در مورد طرف های خوب و بد استفاده از d flip-flops در طرح های شما صحبت می کند.کاتالوگ

یک فلیپ فلاپ چیست؟

بوها d flip-flop (کوتاه برای "داده" یا "تأخیر" تلنگر فلاپ) یک ساختمان اساسی در الکترونیک دیجیتال است که برای ذخیره یک بیت از اطلاعات باینری استفاده می شود.این کار با زمان بندی دقیق ، ضبط و نگه داشتن داده ها فقط در صورت تغییر سیگنال ساعت معمولاً بسته به طراحی ، معمولاً در لبه در حال افزایش یا در حال سقوط عمل می کند.هنگامی که لبه ساعت وارد می شود ، مقدار موجود در ورودی D (داده) به خروجی منتقل می شود ، برچسب Q. پس از این ، خروجی ثابت می شود ، حتی اگر ورودی داده تغییر کند ، تا لبه ساعت معتبر بعدی.

شکل 2. نمودار بلوک D Flip Flop

دو حالت اصلی کار وجود دارد: همزمان و ناهمزمان.در حالت همزمان، F Flip-Flop فقط به سیگنال های ساعت پاسخ می دهد و از تمام قسمت های تغییر مدار در یونیسون اطمینان می دهد.در حالت ناهمزمان، ورودی های اضافی مانند از پیش تعیین شده یا پاک می توانند بدون انتظار برای ساعت ، حالت خروجی را نادیده بگیرند و امکان تنظیم سریع یا تنظیم مجدد را فراهم می کنند.یک فلیپ فلاپ استاندارد D دارای دو ورودی است: داده (D) و ساعت (CLK).در طول یک لبه ساعت فعال ، مقدار ورودی را ضبط می کند.هنگامی که ساعت غیرفعال است ، خروجی ثابت می شود.

چگونه یک فلیپ فلاپ کار می کند؟

A D Flip-Flop ، که معمولاً به عنوان "داده" یا "تأخیر" فلیپ فلاپ شناخته می شود ، با همگام سازی با سیگنال ساعت کار می کند.مکانیسم اصلی آن ساده است: مقدار ورودی (D) را در یک انتقال ساعت خاص (به طور معمول لبه در حال افزایش) نمونه می کند و آن مقدار را به خروجی (Q) منتقل می کند.خروجی مکمل (Q ′) معکوس Q را در خود جای داده است. زیرا فقط در لبه ساعت پاسخ می دهد ، D Flip-Flop یک عنصر ذخیره سازی قابل اعتماد در مدارهای دیجیتال است.

شکل 3. مدار منطق یک flip-flop d

در داخل ، فلیپ فلاپ های D اغلب با استفاده از پیکربندی دروازه های منطق در یک مجموعه چتره یا مخزن دروازه ساخته می شوند.نمودار ارائه شده ، یک قفل دروازه D مبتنی بر NAND را نشان می دهد ، که به طور مشابه عمل می کند.ورودی های اصلی D (داده) و CLK (ساعت) هستند و خروجی ها Q و Q هستند.هنگامی که CLK کم است ، مدار تغییرات D را نادیده می گیرد و خروجی جریان را حفظ می کند.هنگامی که CLK بالا می رود ، مدار به روز می شود: اگر D زیاد باشد ، Q زیاد می شود و Q ′ کم می شود.اگر D کم باشد ، Q کم می شود و Q ′ زیاد می شود.هنگامی که ساعت به کم باز می گردد ، خروجی بسته می شود و حالت خود را تا پالس ساعت بعدی حفظ می کند.

یک جدول حقیقت به روشن شدن این رفتار کمک می کند.هنگامی که ساعت غیرفعال است یا در حال انتقال نیست ، Q و Q ′ ثابت نگه می دارند.در لبه افزایش ساعت ، Q مقدار فعلی D را می گیرد (1 اگر D زیاد باشد ، 0 اگر D کم باشد) در حالی که Q ′ معکوس می شود.این پاسخ ناشی از لبه تضمین می کند که فقط داده های موجود در لبه ساعت ذخیره می شوند ، و باعث می شود که فلیپ فلاپ پایدار و مقاوم در برابر نویز یا تغییرات ورودی سریع بین چرخه ساعت باشد.

D جدول حقیقت فلیپ فلاپ

|

کلوچه |

د |

س (حالت بعدی) |

س ' |

|

0 (کم) |

x |

س (بدون تغییر) |

س ' |

|

↑ (افزایش لبه) |

0 |

0 |

1 |

|

↑ (افزایش لبه) |

1 |

1 |

0 |

|

1 (بالا ، بدون لبه) |

x |

س (بدون تغییر) |

س ' |

این جدول نشان می دهد که یک فلیپ فلاپ خروجی خود را فقط در لبه در حال افزایش سیگنال ساعت به روز می کند که وقتی ساعت از پایین به بالا منتقل می شود.در هر زمان دیگر ، خروجی قبلی خود را حفظ می کند ، و هرگونه تغییر در ورودی داده را نادیده می گیرد.این رفتار قابل پیش بینی و حساس به لبه باعث می شود D flip-flop در سیستم های دیجیتالی که در آن زمان بندی دقیق و کنترل توالی مورد نیاز است ، ارزشمند باشد.

با استفاده از d flip-flops به عنوان چفت داده

فراتر از نقش آنها در کنترل زمان بندی ، F Flip-Flops نیز به عنوان قفل داده عمل می کند.یک قفل داده مقدار ورودی را در یک زمان خاص نگه می دارد و تا زمان لازم آن را پایدار نگه می دارد.این برای جداسازی یک قسمت از مدار از دیگری یا حفظ داده ها در هنگام پردازش مفید است.قفل بر اساس یک ساعت یا فعال کردن سیگنال کار می کند.هنگام فعال بودن ، ورودی را به خروجی منتقل می کند.در صورت غیرفعال بودن ، بدون در نظر گرفتن تغییرات ورودی بیشتر ، خروجی فعلی را در محل قفل می کند.

دستگاه هایی مانند 74LS74 (TTL) و 4042 (CMOS) نمونه هایی از مدارهای یکپارچه حاوی چندین فلیپ D هستند.این دستگاه ها می توانند برای ساخت رجیسترهای حافظه یا واحدهای کنترل گروه بندی شوند.هنگامی که چندین فلیپ فلاپ توسط همان سیگنال کنترل ایجاد می شود ، می توانند مقادیر داده های چند بیتی را ذخیره کنند و به عنوان یک مکان نگهدارنده موقت برای اطلاعات دیجیتال عمل کنند.

قفل داده 4 بیتی

شکل 4 قفل داده 4 بیتی

قفل داده 4 بیتی نشان داده شده در نمودار از چهار فلیپ فلاپ از نوع D (برچسب FFA به FFD) تشکیل شده است که هر یک مسئول ذخیره یک بیت از ورودی باینری 4 بیتی هستند.این فلیپ فلاپ ها به صورت موازی تراز شده و توسط یک سیگنال ساعت مشترک هدایت می شوند ، و از هر چهار مقادیر ورودی مربوطه خود به طور همزمان در یک لبه ساعت استفاده می کنند.

هر فلیپ فلاپ یک بیت ورودی جداگانه (A ، B ، C و D) دریافت می کند و مقدار ذخیره شده را از طریق خروجی Q خود خروجی می کند.هنگامی که پالس ساعت فعال است ، مقادیر ورودی فعلی در فلیپ فلاپ ها بسته می شوند.پس از چسبیدن ، این مقادیر تا زمان رسیدن پالس ساعت بعدی پایدار و در دسترس باقی می مانند ، به طور موثری داده ها را نگه می دارد یا "چسباندن" می کند.

این ساختار قفل را قادر می سازد به عنوان یک ثبت 4 بیتی جمع و جور یا واحد ذخیره سازی داده موقت خدمت کند.این سیستم در سیستم های دیجیتالی که نیاز به انتقال داده های هماهنگ ، مانند واحدهای منطق حسابی ، خطوط لوله دستورالعمل یا اتوبوس های آدرس دارند ، بسیار ارزشمند است.با گرفتن داده ها بر روی یک سیگنال ساعت مشترک ، قفل کنترل دقیق بر زمان ذخیره داده ها و جابجایی در یک مدار را تضمین می کند.

قفل داده شفاف

بر خلاف فلیپ فلاپ های ناشی از لبه ، یک قفل شفاف به طور مداوم داده های ورودی را به خروجی منتقل می کند تا زمانی که سیگنال فعال آن فعال باشد.این رفتار آن را برای برنامه هایی که در آن جریان داده مورد نیاز است ایده آل می کند تا زمانی که یک فرمان خروجی فعلی را منجمد کند.

74LS373 یک چفت شفاف معمولی است.هنگامی که سیگنال فعال آن زیاد است ، داده ها از ورودی به زمان به زمان جریان می یابد.هنگامی که سیگنال Enable کم می شود ، خروجی های جریان قفل می شوند ، تحت تأثیر تغییر در ورودی.

این نوع قفل اغلب شامل خروجی های سه حالت است که در صورت عدم نیاز می توانند از یک اتوبوس مشترک جدا شوند.این مانع از درگیری سیگنال می شود و چندین دستگاه را قادر می سازد از همان خطوط داده بدون تداخل استفاده کنند.قفل های شفاف در مدارهای دسترسی به حافظه ، منطق demultiplexing و سیستمهایی که نیاز به ضبط داده های موقتی اما قابل اعتماد دارند ، متداول است.

قفل داده 8 بیتی

شکل 5 قفل داده 8 بیتی

قفل داده های 8 بیتی که در بالا به تصویر کشیده شده بر اساس اصول چترهای کوچکتر با درج هشت فلیپ فلاپ موازی D ، قادر به ذخیره کل بایت از داده های D0 تا D7 است.این مجموعه معمولاً در مدارهای مجتمع مانند 74LS373 مشاهده می شود.هر هشت فلیپ فلاپ در یک بلوک قفل گروه بندی می شوند ، که داده های ورودی را در لبه در حال افزایش سیگنال ساعت مشترک (CLK) ضبط می کند.هنگامی که ساعت فعال است و خط فعال (EN) ادعا می شود ، مقادیر ورودی فعلی بسته می شوند و در دسترس خروجی قرار می گیرند.

متصل به قفل یک مرحله خروجی سه حالت است.این ویژگی به خروجی ها (Q0 تا Q7) اجازه می دهد تا خطوط داده را هدایت کنند یا بسته به کنترل فعال کننده خروجی (OE) ، یک حالت آمپسل (HI-Z) را وارد کنند.این رفتار سه حالت برای سیستمهایی که شامل اتوبوس های داده مشترک هستند ، مهم است ، زیرا در صورت دسترسی به چندین دستگاه به همان خطوط ، از برخورد سیگنال جلوگیری می کند.قفل های 8 بیتی مانند این در سیستم های دیجیتالی برای همگام سازی و ذخیره موقت داده های گسترده بایت بسیار عالی هستند.آنها اغلب در رابط های ریز پردازنده ، قفل آدرس حافظه و دستگاه های I/O یافت می شوند ، جایی که به عنوان واسطه بین منابع داده سریع و اجزای سیستم کندتر یا هماهنگ عمل می کنند.

کاربردهای D flip-flops

D Flip-Flops در بسیاری از سیستم های دیجیتال بسیار مهم است.آنها به پیگیری زمان بندی و ذخیره صحیح داده ها کمک می کنند ، که برای مواردی مانند نگه داشتن رویدادها به ترتیب ، اطمینان از صفحات سیگنال ها و نگه داشتن داده ها برای مدت کوتاهی مفید است.از تراشه های رایانه ای گرفته تا دستگاه هایی که داده ها را ارسال و دریافت می کنند ، d flip-flops بخش اصلی عملکرد الکترونیک مدرن است.

d flip-flop برای ذخیره سازی داده ها

شکل 6. d flip-flop برای ذخیره سازی داده ها

این شکل گروهی از فلیپ های d را که به طور موازی متصل هستند ، نشان می دهد که هر یک از آنها یک بیت داده (D0 تا D3) را ذخیره می کنند.با هم ، آنها یک ثبت 4 بیتی تشکیل می دهند.همه فلیپ فلاپ ها همان سیگنال ساعت (CLK) را به اشتراک می گذارند ، بنابراین وقتی یک پالس ساعت وارد می شود ، تمام ورودی ها به طور همزمان ذخیره می شوند و به خروجی ها (Q0 تا Q3) ارسال می شوند.ثبت هایی از این دست در ALUS برای ذخیره نتایج ، در سیستم های I/O برای نگه داشتن داده ها در حین نقل و انتقالات و در واحدهای کنترل برای پیگیری دستورالعمل ها استفاده می شود.از آنجا که فلیپ فلاپ ها تحریک شده اند ، داده ها را دقیقاً در هر لبه ساعت ذخیره می کنند ، که به زمان بندی دقیق کمک می کند.حتی اگر این نوع ذخیره سازی موقتی باشد (داده ها هنگام خاموش شدن برق از بین می روند) ، بسیار سریع است و آن را برای بافر و حافظه کوتاه مدت مفید می کند.

d flip-flops برای انتقال داده

شکل 7 فلیپ فلاپ ها برای انتقال داده ها

شکل نشان می دهد که d flip-flops متصل به یک زنجیره برای تشکیل یک رجیستری شیفت.داده ها از طریق ورودی داده های سریال یک بیت وارد یک بیت می شوند و از یک فلیپ فلاپ به حالت دیگر با هر پالس تغییر (سیگنال ساعت) منتقل می شوند.هر فلیپ فلاپ ، گام به گام ، داده ها را در کنار هم قرار می دهد.این روش انتقال داده ها ارتباطات سریال نامیده می شود.این بیماری معمولاً در سیستمهایی مانند درایورهای LED ، UARTS (انتقال دهنده های گیرنده ناهمزمان جهانی) و ژنراتورهای سیگنال استفاده می شود.رجیسترهای شیفت مانند این نیز می توانند پیشرفته تر مانند انواع دو طرفه یا دایره ای برای کارهای خاص مانند رمزگذاری داده ها یا اضافه کردن تأخیر انجام شوند.از آنجا که داده ها به روشی کنترل شده و بیت بیت حرکت می کنند ، این تنظیم برای دستگاه هایی با پهنای باند محدود یا مسافت های طولانی برای ارسال سیگنال کارآمد است.

تقسیم فراوانی

شکل 8 تقسیم فرکانس

شکل نشان می دهد که چگونه یک فلیپ فلاپ می تواند یک فرکانس ورودی را تقسیم کند.با اتصال خروجی Q 'به ورودی D ، Flip-Flop حالت خود را در هر پالس ساعت قرار می دهد.در نتیجه ، فرکانس خروجی نیمی از فرکانس ورودی (f/2) می شود.این روش اغلب برای ساخت تقسیم کننده فرکانس استفاده می شود.با زنجیر کردن فلیپ فلاپ های بیشتر ، می توانید بخش های تقسیم به 4 ، تقسیم به 8 یا بالاتر را در ساعتهای دیجیتال ، ژنراتورهای نرخ Baud و مدارهای نمونه گیری مفید ایجاد کنید.این رویکرد ساده ، قابل اعتماد و از حداقل سخت افزار است و آن را برای دستیابی به زمان بندی در سیستم های دیجیتال ایده آل می کند.

پیشخوان و تایمر

D Flip-Flops بلوک های ساختمانی در پیشخوان های دیجیتال و مدارهای زمان بندی است.هنگامی که به صورت سری ترتیب داده می شوند ، می توانند پیشخوان های باینری یا دهه را تشکیل دهند که با هر پالس ساعت ، خروجی آنها را افزایش می دهد.این پیشخوان ها به طور گسترده در ساعتهای دیجیتال ، پیشخوان فرکانس و مدارهای تایمر برای اندازه گیری زمان سپری شده ، وقایع شمارش یا تولید سیگنال های کنترل به موقع استفاده می شوند.در برنامه های تایمر ، Flip-Flops با تقسیم فرکانس ساعت به فواصل طولانی تر و قابل کنترل تر ، به تأخیرهای دقیق کمک می کند.به دلیل ماهیت ناشی از لبه آنها ، فلاپ های D اطمینان حاصل می کنند که شمارش و انتقال زمان دقیقاً در لحظه های مناسب اتفاق می افتد و خطر ابتلا به اشکالات یا خطاهای زمان بندی را در مدارهای حساس کاهش می دهد.

ارتباطات و رابط اتوبوس

در سیستم های ارتباطی دیجیتال ، داده ها اغلب باید به طور موقت ، هماهنگ یا بین مؤلفه های کار شده با سرعت های مختلف ذخیره شوند.D Flip-Flops در این کارها نقش دارد.آنها در ثبت های شیفت برای تبدیل داده ها بین قالب های سریال و موازی در پروتکل هایی مانند UART ، SPI و I²C استفاده می شوند.علاوه بر این ، در رابط اتوبوس ، D Flip-Flops به داده های چسباندن در هنگام انتقال کمک می کند ، و اطمینان می دهد که اطلاعات به اندازه کافی پایدار نگه داشته می شوند تا در یک خط اتوبوس خوانده شوند یا نوشته شوند.آنها همچنین در از بین بردن عدم تطابق زمان بندی بین قسمت های مختلف یک سیستم ، ارتباطات را قابل اطمینان تر می کنند ، به خصوص در سیستم هایی با دستگاه های مختلف که خطوط داده را به اشتراک می گذارند.

سیستم های تعبیه شده

در برنامه های تعبیه شده ، Flip-Flops برای ذخیره سیگنال های کنترل ، ورودی های سنسور قفل و ردیابی وضعیت زیر سیستم های دیجیتال در میکروکنترلرها یا پردازنده ها استفاده می شود.توانایی آنها در حفظ داده ها تا چرخه ساعت بعدی ، عملکرد پایدار را حتی هنگام کار با سیگنال های پر سر و صدا یا به سرعت در حال تغییر تضمین می کند.D Flip-Flops با پشتیبانی از ایجاد مدارهای منطقی قابل پیش بینی ، از جمله دستگاه های دولتی ، کنترل کننده های دنباله و مدارهای زمان بندی ، به دستیابی به این هدف کمک می کند.آنها همچنین در تولید پالس ، سیگنال های دروازه و همگام سازی حوادث استفاده می شوند.

مزایای D flip-flops

• ورودی تک داده (D)

D Flip-Flops دارای یک ورودی داده واحد است که به سادگی به عنوان "D" شناخته می شود که طراحی مدار دیجیتال را ساده می کند.بر خلاف SR یا JK Flip-Flops که به چندین ورودی نیاز دارند و منطق اضافه شده برای مدیریت حالت های مختلف ، D Flip-Flop فقط با یک ورودی داده و یک سیگنال ساعت کار می کند.این باعث می شود پیچیدگی طراحی کاهش یابد ، خطاها را در واگذاری منطق به حداقل برساند و مسیریابی سیگنال را در مدارهای یکپارچه ساده می کند.این سیستم در سیستم هایی که نیاز به کنترل دقیق داده ها دارند ، مانند رجیسترها ، واحدهای حافظه و طرح های مهم و مهم ، سودمند است.

• اجتناب از کشورهای نامعتبر

قدرت کلیدی D flip-flops توانایی آنها در جلوگیری از حالتهای تعریف نشده است ، یک مسئله مشترک در SR Flip-Flops در هنگام تنظیم و تنظیم مجدد همزمان همزمان.d flip-flops این کار را با استفاده از وارونگی منطقی بین سیگنال های کنترل داخلی کنار می گذارد ، و اطمینان می دهد که تنها یک شرایط کنترل در یک زمان فعال است.این انتخاب طراحی باعث افزایش قابلیت اطمینان و قوام ، در محیط های ایمنی یا با دقت بالا می شود.

• مصرف انرژی پایین

D Flip-Flops با انرژی کارآمد است و آنها را برای برنامه های کم مصرف مانند الکترونیک قابل حمل و دستگاه های باتری ایده آل می کند.آنها غالباً از ساعت کاری مشروط (فقط در صورت تغییر داده ها) و سایر بهینه سازی ها برای کاهش سوئیچینگ غیر ضروری استفاده می کنند و باعث کاهش مصرف برق می شوند.با داشتن دروازه های داخلی کمتر در مقایسه با فلیپ فلیپ های پیچیده تر مانند نوع JK ، آنها از دست دادن قدرت استاتیک و پویا نیز به حداقل می رسند.

• رفتار دو کشور پایدار

مانند همه فلیپ فلاپ ها ، F Flip-Flops به صورت دو پایدار کار می کنند ، آنها می توانند یکی از دو حالت خروجی (0 یا 1) را نگه دارند تا سیگنال ساعت بعدی باعث تغییر شود.این به آنها اجازه می دهد تا به عنوان واحدهای حافظه تک بیتی ، برای منطق پی در پی ، ثبت های تغییر ، پیشخوان و دستگاه های دولتی عمل کنند.توانایی آنها در حفظ داده ها بدون طراوت ثابت به حفظ جریان کنترل قابل اعتماد در مدارهای دیجیتال کمک می کند.

• ساختار داخلی ساده

پیکربندی داخلی یک flip-flop d نسبتاً ساده است ، که اغلب از چفت های SR و یک اینورتر برای دقت زمان بندی تشکیل شده است.این در تضاد با Flip-Flops JK یا T است که به بازخورد پیچیده تر و منطق کنترل نیاز دارند.سادگی d flip-flops باعث می شود که آنها اجرای ، تأیید و اشکال زدایی را آسان تر کنند و رفتار قابل پیش بینی آنها باعث می شود آنها به یک انتخاب برتر در فرآیندهای طراحی خودکار تبدیل شوند.

• عمل با سرعت بالا

طراحی شده برای عملکرد ، d flip-flops به دلیل مدار داخلی کارآمد و سوئیچینگ منطق سریع ، تأخیر در انتشار حداقل را ارائه می دهد.این امر باعث می شود آنها برای برنامه های پر سرعت ، مانند پردازش سیگنال دیجیتال و پروتکل های ارتباطی ، ایده آل شوند.طبیعت ناشی از لبه آنها همگام سازی دقیق با سیگنال های ساعت را تضمین می کند.

• کارایی جزء

D Flip-Flops دارای منابع کارآمد است و به دروازه های منطقی و ترانزیستور کمتری نسبت به سایر انواع نیاز دارد.این طرح جمع و جور به منطقه تراشه کوچکتر ، کاهش هزینه ها و پتانسیل تراکم ادغام بالاتر در ICS ترجمه می شود.حداقل استفاده آنها از مؤلفه ها همچنین منجر به اثرات انگل پایین تر می شود و باعث افزایش سرعت و بهره وری انرژی برای سیستم های دیجیتالی در مقیاس بزرگ و با کارایی بالا می شود.

مضرات d flip-flops

• عدم وجود مکانیسم های بازخورد داخلی

D Flip-Flops برای ذخیره یک بیت واحد از داده ها صرفاً بر اساس سیگنال های ورودی و ساعت ساخته شده است و فاقد هرگونه قابلیت بازخورد ذاتی است.این بدان معنی است که آنها نمی توانند بر اساس حالت های قبلی یا منطق داخلی ، خروجی خود را تنظیم کنند.در برنامه هایی که بازخورد مانند سیستم های کنترل حرکتی ، حلقه های PID یا فیلتر سازگار مورد نیاز است ، برای شبیه سازی بازخورد باید مدار خارجی معرفی شود.به عنوان مثال ، اتصال خروجی به دروازه های منطق ، پیچیدگی را اضافه می کند ، تعداد مؤلفه ها را افزایش می دهد و تجزیه و تحلیل زمان بندی را پیچیده می کند ، به طور بالقوه پاسخ و ثبات سیستم را کاهش می دهد.

• بدون عملکرد ضامن بومی

D Flip-Flops ذاتاً خروجی خود را با هر پالس ساعت تغییر نمی دهد.درعوض ، آنها ورودی را در لبه تحریک ساعت آینه می کنند.این باعث می شود آنها برای استفاده مستقیم در پیشخوان ها یا تقسیم کننده های فرکانس ، که در آن رفتار جابجایی مورد نیاز است ، نامناسب باشد.تقلید یک فلیپ فلاپ با اتصال خروجی معکوس به ورودی داده می تواند کار کند ، اما این باعث می شود سیم کشی اضافی اضافه شود ، حساسیت به مسائل مربوط به یکپارچگی را افزایش می دهد و برای جلوگیری از شرایط مسابقه به ویژه در مدارهای پر سرعت ، نیاز به زمان بندی دقیق دارد.

• تأخیر انتشار

مانند همه فلیپ فلاپ ها ، انواع D تأخیر انتشار را معرفی می کنند ، زمان بین یک لبه ساعت و تغییر خروجی مربوطه.در حالی که غالباً در محدوده نانو ثانیه ، این تأخیر می تواند در سیستم های پر سرعت یا عمیقاً خط لوله جمع شود ، که به طور بالقوه باعث تخلفات زمان بندی ، اشکالات یا شکاف می شود.تجزیه و تحلیل زمان بندی دقیق ، اغلب با ابزارهای شبیه سازی و نمودارهای زمان بندی دقیق ، در چنین طرح هایی برای اطمینان از ثبات و صحت استفاده می شود.

• حساسیت زمان را تنظیم و نگه دارید

D Flip-Flops نیاز به ورودی داده ها برای یک پنجره کوتاه قبل و بعد از لبه ساعت ، معروف به تنظیم و زمان نگه داشتن دارد.اگر این نیاز نقض شود مانند زمانی که انتقال داده ها خیلی نزدیک به ساعت اتفاق می افتد ، ممکن است خروجی های نادرست یا غیرقابل پیش بینی منجر شود.در طرح های پر سرعت یا پیچیده ، تحقق این محدودیت های زمان بندی می تواند چالش برانگیز باشد ، که اغلب نیاز به استفاده از بافرها یا تعادل مسیر دقیق ، افزایش پیچیدگی طراحی و کاهش حاشیه زمان بندی دارد.

• خطر متلاشی بودن

قابلیت متلاشی شدن هنگامی اتفاق می افتد که فلیپ فلاپ انتقال ورودی را خیلی نزدیک به لبه ساعت ، اغلب از منابع ناهمزمان دریافت می کند ، و باعث می شود که وارد یک حالت ناپایدار شود که ممکن است زمان برطرف شود.در این دوره ، خروجی ممکن است نوسان داشته باشد یا سطح منطق نامشخصی را تولید کند.این در سیستم هایی که رفتار قطعی مهم است ، مانند هنگام عبور از حوزه های ساعت ، خطرناک است.برای کاهش این موضوع ، از مدارهای هماهنگ کننده یا فلیپ فلاپ ها استفاده کنید که برای رسیدگی به قابلیت متلاطم تر طراحی شده اند.

• قابلیت داخلی محدود

در حالی که ساده و به طور گسترده ای استفاده می شود ، d flip-flops فقط عملکرد اصلی قفل کردن داده ها را ارائه می دهد.در مقابل ، FLIP-FLOPS JK یا SR از عملیات پیچیده تری مانند شرایط جابجایی یا تنظیم/تنظیم مجدد همزمان بدون منطق اضافی پشتیبانی می کند.D Flip-Flops همچنین غالباً فاقد ورودی های غیر همزمان و ورودی های واضح است ، مگر اینکه به طور خاص در آن طراحی شده باشد ، انعطاف پذیری آنها را در سناریوهای کنترل خاص محدود می کند.برای برنامه های کاربردی که نیاز به رفتار ظریف تر در یک چرخه ساعت واحد دارند ، دروازه ها و منطق اضافی باید D Flip-Flops ، افزایش پیچیدگی مدار و تلاش طراحی را تکمیل کنند.

پایان

D Flip-Flops در الکترونیک دیجیتال بسیار مفید است زیرا می توانند داده ها را ذخیره کرده و با استفاده از سیگنال های ساعت آن را پایدار نگه دارند.آنها برای استفاده ساده هستند ، از خطاهایی مانند حالت های نامعتبر جلوگیری می کنند و در سیستم های سریع و کم مصرف به خوبی کار می کنند.می توانید از آنها در مدارهای ثبت نام ، چفت ، پیشخوان و مدارک انتقال داده استفاده کنید.آنها همچنین در سیستمهایی مانند میکروکنترلرها و دستگاههای ارتباطی مفید هستند.اما آنها دارای برخی از نقاط ضعف هستند ، مانند تأخیر در زمان پاسخ ، نیاز به زمان بندی دقیق و نداشتن بازخورد داخلی یا عملکردهای ضامن.دانستن هم نقاط قوت و هم ضعف در طراحی سیستم های دیجیتال بهتر کمک می کند.

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

سوالات متداول [FAQ]

1. فرم استاندارد D flip-flop چیست؟

A D Flip-Flop دارای سه قسمت اصلی است: ورودی داده (D) ، یک ورودی ساعت (CLK) و دو خروجی (Q و Q ′).این کار با کپی کردن مقدار از ورودی D به خروجی Q فقط در صورت تغییر سیگنال ساعت ، معمولاً در لبه در حال افزایش (از پایین به بالا) کار می کند.پس از آن لحظه ، خروجی حتی اگر ورودی تغییر کند ، یکسان باقی می ماند.این تنظیم باعث می شود d flip-flop برای ذخیره یک بیت اطلاعات در یک زمان خاص مفید باشد.فلیپ فلاپ استاندارد D ساده و قابل اعتماد است و آن را در مدارهای حافظه و سیستم های دیجیتال متداول می کند.

2. معادله d flip-flops چیست؟

قانون اصلی برای یک فلیپ فلاپ ساده است: هنگام تغییر سیگنال ساعت ، خروجی Q با ورودی D برابر می شود.این می تواند به صورت Q (Next) = D. نوشته شود این بدان معنی است که هر مقدار در ورودی D در لحظه ای که لبه ساعت رخ می دهد به خروجی Q منتقل می شود.Flip-Flop تمام تغییرات دیگر را تا لبه ساعت بعدی نادیده می گیرد.این امر باعث می شود d flip-flops در طرح های دیجیتال استفاده و درک آن آسان شود.

3. فرکانس خروجی D flip-flop چیست؟

اگر ورودی D را به مقابل خروجی Q (Q ′) وصل کنید ، D Flip-Flop هر بار که سیگنال ساعت کیک می کند ، حالت خود را تغییر می دهد.این باعث می شود فرکانس خروجی نیمی از فرکانس ساعت باشد.بنابراین ، اگر ساعت 8 مگاهرتز باشد ، خروجی 4 مگاهرتز می شود.این تنظیم اغلب در مدارها برای تقسیم فرکانس ، مانند تایمرها یا پیشخوان ها استفاده می شود.

4. تفاوت بین F Flip-Flops چیست؟

D Flip-Flop هنگام تغییر ساعت ، ورودی (d) را به خروجی (q) کپی می کند.از آن برای ذخیره داده ها استفاده می شود.T Flip-Flop متفاوت کار می کند ، هر بار که ساعت کیک می کند ، خروجی خود را تغییر می دهد یا "تغییر می دهد" ، اما فقط در صورتی که ورودی T زیاد باشد.اگر T کم باشد ، هیچ اتفاقی نمی افتد.d flip-flops برای نگه داشتن داده ها استفاده می شود ، در حالی که از فلیپ فلاپ ها برای ساخت پیشخوان و تقسیم سیگنال های ساعت استفاده می شود.آنها حتی اگر هر دو توسط یک ساعت ایجاد شوند ، متفاوت رفتار می کنند.

5. تفاوت بین AT و D Flip-Flop چیست؟

هیچ فلیپ فلاپ استاندارد به نام "در Flip-Flop" وجود ندارد.این ممکن است یک اشتباه یا یک تایپی باشد ، احتمالاً به معنای گفتن "t flip-flop" است.اگر اینگونه باشد ، تفاوت ساده است: A D Flip-Flop مقدار را در ورودی D در هنگام کیک کردن ساعت ذخیره می کند ، در حالی که یک Flip-Flop در صورت بالا بودن ورودی T ، خروجی خود را (سوئیچ بین 0 تا 1) می کند.بنابراین ، فلیپ فلاپ ها برای ذخیره داده ها هستند و فلیپ فلاپ ها برای حالت های تعویض هستند.اگر "در" به معنای چیز دیگری باشد ، باید واضح تر توضیح داده شود.

نمای کلی از FPGA XC4044XL-3BG432C

در 2025/06/2

راهنمای شما برای MPC8247CZQTiea از Freescale

در 2025/05/30

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147750

-

pinout uSB-C و ویژگی های

در 2000/04/18 111921

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111349

-

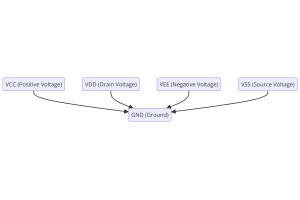

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83714

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79502

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66872

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63005

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 62954

-

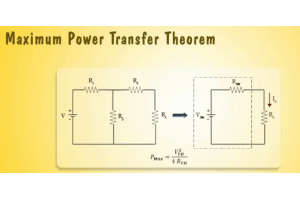

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54078

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52092