منطق پی در پی: اصول ، دستگاه ها ، چالش ها و روش های بازرسی

این راهنما به بررسی مدارهای منطقی پی در پی ، تجزیه و تحلیل اصول ، انواع و کاربردهای آنها می پردازد.این توضیح می دهد که چگونه حافظه و منطق با هم کار می کنند و این مدارها را در سیستم های دیجیتالی مدرن مهم می کند.شما در مورد پیشخوان ها ، ثبت ها و ژنراتورهای پالس و همچنین نحوه رسیدگی به چالش هایی مانند مشکلات ساعت ، مشکلات تنظیم مجدد و تخریب سیگنال می آموزید.این که آیا شما در حال رفع گسل ها هستید یا طرح ها را بهبود می بخشید ، این راهنما نکات و استراتژی های عملی را برای کمک به شما در مدارهای منطقی پی در پی ارائه می دهد.کاتالوگ

مقدمه

مدارهای منطق متوالی جنبه مهمی از طراحی دیجیتال هستند که با توانایی آنها در حفظ حافظه و تولید خروجی ها بر اساس ورودی های فعلی و حالت های تاریخی متمایز است.بر خلاف مدارهای ترکیبی ، که فقط به ورودی های موجود متکی هستند ، مدارهای متوالی اجزای حافظه را که حالت های گذشته را ذخیره می کنند ، ادغام می کنند و رفتار پویا و سازگار را قادر می سازند.رابطه بین ورودی ، حافظه و خروجی اغلب در نمودارهای بلوک نشان داده می شود ، و حالت مدار از طریق مکانیسم بازخورد بیان شده به عنوان Qn+1 = F (x ، qn) در حال تحول است ، جایی که x ورودی است.مدارهای پی در پی به چفت ها طبقه بندی می شوند ، که به طور مداوم به ورودی ها پاسخ می دهند ، و فلیپ فلاپ ها ، که توسط سیگنال های ساعت هماهنگ می شوند.این مدارهای محور حافظه در برنامه هایی مانند ذخیره داده ها و دستگاه های دولتی نقش دارند ، جایی که زمان بندی و حفظ حالت برای عملکرد سیستم است.درک تعامل حافظه و منطق در این مدارها برای طراحی سیستم های دیجیتال کارآمد و پیشرفته مهم است.

سه دستگاه منطقی

مدارهای منطقی پی در پی برای معماری سیستم های دیجیتالی معاصر بسیار عالی هستند ، با طبقه بندی آنها اغلب به عملکردهای منطق متمایز وابسته است.در این بخش به بررسی سه دستگاه کلیدی که ویژگی های اصلی مدارهای منطقی پی در پی را در بر می گیرد ، به کار می رود و به برنامه های کاربردی و مکانیسم های عملیاتی آنها می پردازد.

پیشرو

در هسته آن ، یک پیشخوان شامل فلیپ فلاپ هایی است که در پالس های ورودی (CP) مهارت دارند.خروجی یک پیشخوان ذاتاً با وضعیت فعلی آن گره خورده است ، و حداکثر شمارش پالس های ورودی به عنوان "مدول" گفته می شود که به عنوان M. به عنوان مثال ، یک پیشخوان با M = 6 به عنوان یک پیشخوان شش ضلعی مشخص می شود.تعامل بین ظرفیت شمارش و برنامه های کاربردی."Modulo" تعداد حالتهای معتبری را که پیشخوان می تواند برای انواع کاربردها مانند ساعتهای دیجیتال و تقسیم کننده فرکانس نمایش دهد ، مشخص می کند.

پیشخوان ها را می توان بر اساس خصوصیات متنوع ، از جمله سیستم شمارش (باینری ، اعشاری ، دلخواه) ، جهت شمارش (بالا ، پایین ، برگشت پذیر) و همگام سازی (ناهمزمان در مقابل هماهنگ) طبقه بندی کرد.هر طبقه بندی نقش خاصی را در طراحی دیجیتال انجام می دهد ، و این امکان را برای انتخاب مناسب ترین نوع برای برنامه های خاص دارد.پیشخوان های همزمان به دلیل ویژگی های زمان بندی قابل پیش بینی آنها اغلب در سناریوهای پر سرعت مورد علاقه قرار می گیرند ، در حالی که پیشخوان های ناهمزمان ممکن است جای خود را در طرح های ساده تری پیدا کنند که سرعت آن کمتر مهم باشد.

ثبت نام

رجیسترها مدارهای تخصصی هستند که برای نگه داشتن اعداد ، نتایج عملکرد یا دستورالعمل ها ساخته شده اند و به عنوان مکان های ذخیره موقت در سیستم های دیجیتال عمل می کنند.زیر مجموعه ای که به عنوان Registrs Shift شناخته می شود ، امکان تغییر جانبی داده های ذخیره شده در پاسخ به پالس های تغییر را فراهم می کند ، امکان دستکاری و انتقال داده ها را فراهم می کند.سازگاری رجیسترها و ثبت های شیفت ، آنها را در رایانه ها و دستگاه های مختلف دیجیتال به آنها می دهد.هر فلیپ فلاپ در یک رجیستری می تواند یک بیت از داده های باینری را ذخیره کند ، و به N Flip-Flops اجازه می دهد تا به طور جمعی بیت های N را حفظ کنند.

ویژگی فلیپ فلاپ ها در ثبت ها ، ظرفیت آنها برای تنظیم مقادیر 0 یا 1 است ، صرف نظر از پیکربندی آنها ، همزمان ، استاد برده یا حاشیه ای.این تطبیق پذیری نیاز به اجرای عملیات پیچیده مانند محاسبات حسابی یا بافر داده است.طراحی رجیسترها می تواند بر عملکرد سیستم ، به ویژه در مورد سرعت و کارآیی تأثیر بگذارد ، زیرا اغلب سرعت دسترسی به داده ها و پردازش را نشان می دهند.

ژنراتور پالس متوالی

یک ژنراتور پالس متوالی دستگاهی است که سیگنال های پالس را در یک توالی از پیش تعیین شده با گذشت زمان ایجاد می کند.این ژنراتورها در سیستم های دیجیتالی بسیار عالی هستند و سیگنال های زمان بندی لازم را ارائه می دهند که دستگاه ها را در انجام محاسبات یا عملیات به ترتیب خاص راهنمایی می کنند.از قابلیت تولید سیگنال های زمان بندی دقیق برای هماهنگ سازی اجزای مختلف در یک سیستم استفاده می شود و اطمینان حاصل می شود که عملیات در دنباله صحیح و در لحظه مناسب آشکار می شود.

به عنوان مثال ، در سیستم های ارتباطی ، این ژنراتورها ممکن است سیگنال های ساعت ایجاد کنند که انتقال داده ها را تنظیم می کند.در سیستم های کنترل ، آنها زمان عملیات مکانیکی را تنظیم می کنند.اثربخشی یک ژنراتور پالس پی در پی می تواند تا حد زیادی بر عملکرد کلی و قابلیت اطمینان یک سیستم دیجیتالی تأثیر بگذارد و تأکید بر ضرورت طراحی و توجه متفکرانه پارامترهای زمان بندی.

ویژگی ها و چالش ها

مدارهای منطقی پی در پی با مدارهای ترکیبی متفاوت هستند زیرا خروجی آنها نه تنها به ورودی های فعلی بلکه به حالت های گذشته نیز بستگی دارد.این توانایی "به یاد آوردن" آنها را قادر می سازد تا توابع مانند فلیپ فلاپ ها ، پیشخوان ها و رجیسترها را کنترل کنند ، که در برنامه های مختلف از تایمرهای اساسی گرفته تا سیستم های دیجیتالی پیشرفته عالی هستند.اعتماد به داده های ورودی تاریخی پیچیدگی را معرفی می کند.به عنوان مثال ، حالت یک فلاپ به ورودی فعلی و وضعیت قبلی آن بستگی دارد و زمان بندی و هماهنگ سازی را ایجاد می کند.تأخیر یا عدم تطابق می تواند باعث ایجاد خطا شود.عیب یابی این مدارها اغلب شامل شبیه سازی ها و روش های آزمایش مانند مشاهده حالت ها و دستکاری ورودی ها برای یافتن اختلافات است.توالی ورودی-خروجی و استفاده از نرم افزار شبیه سازی برای تجزیه و تحلیل رفتار مدار به مرور زمان ، به آنها در شناسایی و حل گسل ها کمک می کند.با درک تعامل ورودی های گذشته و حال ، عملکرد مدارهای متوالی را با اطمینان اطمینان می دهد.

مسائل ساعت: اطمینان از زمان بندی قابل اعتماد

سیگنال های ساعت به عنوان ضربان قلب سیستم های دیجیتال عمل می کنند و هماهنگ سازی دقیق قطعات را تضمین می کنند.خرابی ها ، مانند از دست دادن سیگنال ، رانش (تغییر فرکانس) یا لرزش (نوسانات زمان بندی) ، می تواند عملیات را مختل کند و منجر به خطاها در انتقال داده ها یا خرابی های سیستم شود.برخی دیگر این مشکلات را با افزونگی (چندین منبع ساعت) و ابزارهای نظارتی که علائم اولیه خرابی را تشخیص می دهند ، می پردازند.مدیریت ساعت قوی برای سیستمهایی که به زمان بندی دقیق متکی هستند ، مانند ارتباطات از راه دور یا برنامه های کاربردی خودرو ، مناسب است.مدیریت فعال سیگنال های ساعت ، قابلیت اطمینان و عملکرد را تضمین می کند.

تنظیم مجدد: اهمیت تنظیم مجدد قابل اعتماد

یک تابع تنظیم مجدد سیستم ها پس از خطا ، سیستم ها را به حالت شناخته شده باز می گرداند.سیگنال های تنظیم مجدد ضعیف ناشی از طراحی ضعیف ، قدرت کافی یا تداخل می تواند منجر به اولیه سازی نادرست شود و منجر به رفتار نامنظم یا تصادف شود.برخی دیگر با افزودن مقاومتهای کشش ، کاهش نویز با تکنیک های تسکین دهنده و آزمایش تنظیم مجدد شرایط با استفاده از شبیه سازی ، قابلیت اطمینان را تقویت می کنند.مکانیسم های تنظیم مجدد مؤثر برای پایداری سیستم ، اطمینان از عملکرد صاف و کاهش خطر خرابی در برنامه ها مفید است.

خطاهای اتوبوس: علل و راه حل ها

خطاهای اتوبوس جریان دستورالعمل ها و داده ها را مختل می کند ، که اغلب ناشی از مشکلات درایور (به عنوان مثال ، نرم افزار منسوخ شده) یا سخت افزار معیوب (به عنوان مثال ، حافظه یا رابط) است.این خطاها می توانند عواقب جدی مانند دوزهای پزشکی نادرست یا نقص سیستم مالی داشته باشند.جلوگیری از خطاهای اتوبوس شامل به روزرسانی منظم درایور ، بازرسی های سخت افزاری و استفاده از روش های بررسی خطا مانند بررسی های برابری است.این استراتژی ها به حفظ یکپارچگی داده ها و قابلیت اطمینان سیستم کمک می کنند ، به ویژه در محیط هایی که خرابی ها می توانند تأثیرات شدیدی داشته باشند.

مشکلات قطع: مدیریت چالش های قطع

وقفه ها به ریزپردازنده ها اجازه می دهند تا وظایف را در اولویت قرار دهند اما مواردی مانند سیگنال های کاذب (چسبندگی خط) ، تداخل یا رسیدگی نادرست می توانند اجرای برنامه را مختل کنند.پرداختن به این مشکلات مستلزم محافظت در برابر تداخل ، تکنیک های ردیابی و پالایش پروتکل ها از طریق آزمایش است.سیستم های به خوبی طراحی شده با استفاده از بررسی خطا ، افزونگی و بهبود تکراری ، مسائل مربوط به وقفه را پیش بینی می کنند.این عملکرد قابل اعتماد را حتی در شرایط چالش برانگیز تضمین می کند ، که نشان دهنده اهمیت طراحی و آزمایش دقیق است.

تخریب سیگنال: حفظ یکپارچگی داده ها

اتوبوس های موازی طولانی با مشکلات تخریب سیگنال مانند متقاطع (تداخل بین خطوط) و سر و صدای عوامل محیطی یا تداخل الکترومغناطیسی (EMI) روبرو هستند.این مشکلات می تواند منجر به خطاهای داده و خرابی سیستم شود.بسیاری از تخریب سیگنال های جنگی با محافظ ، سیگنالینگ دیفرانسیل و طراحی دقیق مانند سیم های فاصله یا استفاده از کابل های کوتاه تر.درک و پرداختن به این چالش ها ، ارتباطات قابل اعتماد در سیستم های الکترونیکی ، حتی در شرایط تغییر را تضمین می کند.

روش بازرسی

هنگام ترمیم مدارهای منطقی پی در پی ، مهم است که ابتدا معماری و طراحی مدار سیستم را درک کنید.بازرسی دقیق از گسلها می تواند با کاهش مسائل احتمالی ، عیب یابی را کار کند.در سیستم های پیشرفته مانند دستگاه های پزشکی ، ابزارهای خود تشخیصی داخلی می توانند به شناسایی مشکلات کمک کنند و نشان می دهد که چگونه فناوری می تواند شیوه های نگهداری را تقویت کند.

منبع تغذیه را بررسی کنید

مدارهای منطقی پی در پی اغلب به منبع تغذیه مانند 5 ولت ، 15 ولت یا 12 ولت £ متکی هستند.گسلهایی مانند ولتاژهای ناپایدار یا مدارهای کوتاه می توانند باعث خرابی سیستم مانند عدم پاسخگویی یا رفتار نامنظم شوند.خازن های معیوب علت اصلی مدارهای کوتاه هستند و با استفاده از یک ردیاب فعلی قابل تشخیص هستند.نگه داشتن گزارش عملکرد منبع تغذیه می تواند به پیش بینی مسائل قبل از وقوع کمک کند.

ساعت را بررسی کنید

مدارهای ساعت ، ساخته شده با کریستال کوارتز یا نوسان سازهای RC ، زمان بندی دقیق را تضمین می کنند.کریستال های کوارتز ظریف هستند و باید با دقت مورد بازرسی قرار گیرند.ابزارهایی مانند اسیلوسکوپ ها یا پروب های منطق می توانند فرکانس ، دامنه و فاز سیگنال ساعت را برای شناسایی مشکلات اندازه گیری کنند.ایجاد یک پایه برای رفتار ساعت عادی می تواند تشخیص ناهنجاری ها را آسانتر کند.

اتوبوس را بررسی کنید

برای اطمینان از عملکرد مناسب ، فعالیت پالس را در اتوبوس با یک پروب منطقی تأیید کنید.اگر هیچ فعالیتی یافت نشد ، درایور اتوبوس و سیگنال های ورودی را بررسی کنید.اندازه گیری مقاومت همچنین می تواند به تشخیص مشکلات اتوبوس کمک کند.نگه داشتن سوابق مربوط به خرابی های اتوبوس گذشته می تواند بینش مفیدی برای عیب یابی در آینده فراهم کند.

سیگنال های نبض بحرانی را بررسی کنید

سیگنال های کنترل مانند تنظیم مجدد ، فعال کردن و خواندن حافظه باید با استفاده از پروب های منطقی یا اسیلوسکوپ ها کنترل شوند.سیگنال های سالم نشان می دهد که مدار یکپارچه (IC) به درستی کار می کند ، در حالی که ناهنجاری ها می توانند به غرفه های برنامه یا مشکلات دیگر اشاره کنند.مستند سازی منظم رفتار سیگنال می تواند به تشخیص سریعتر مسائل مکرر کمک کند.

رابط را بررسی کنید

اتصالات سست یا نادرست می تواند باعث ایجاد مشکلات عملکرد شود.تمیز کردن و اتصال مجدد رابط می تواند بسیاری از گسل ها را برطرف کند.خطوط ارتباطی خارجی در برابر تداخل الکترومغناطیسی (EMI) آسیب پذیر هستند ، که می تواند انتقال داده ها را مختل کند.محافظ و شناسایی منابع EMI اقدامات پیشگیرانه مؤثر است.استفاده از یک چک لیست برای بازرسی های رابط ، نگهداری کامل را تضمین می کند.حفظ مدارهای منطقی پی در پی به فنی و درس نیاز دارد.استفاده از بهترین شیوه ها و یادگیری از تعمیرات گذشته می تواند قابلیت اطمینان و کارآیی را در عیب یابی این سیستم ها بهبود بخشد.

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

چگونه EDA گردش کار طراحی الکترونیک را تغییر می دهد؟

در 2024/12/31

JPEG توضیح داد: اصول ، مزایا و برنامه ها

در 2024/12/31

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147776

-

pinout uSB-C و ویژگی های

در 2000/04/18 112022

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111351

-

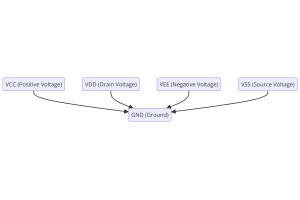

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83777

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79577

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66964

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63104

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63041

-

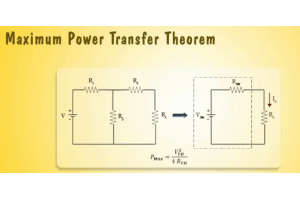

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54097

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52190