LVPECL توضیح داد: راهنمایی برای منطق همراه با ولتاژ کم ولتاژ

منطق همراه با ولتاژ کم ولتاژ (LVPECL) به عنوان یک پیشرفت کلیدی در فناوری منطق دیجیتال ، متناسب با پاسخگویی به خواسته های محیط های کم ولتاژ است.با استفاده از 3.3 ولت یا 2.5 ولت ، LVPECL از منطق سنتی همراه با امیتر همراه (PECL) تکامل می یابد ، که به منبع تغذیه 5.0 ولت متکی است.این تغییر تأکید روزافزون بر راه حل های کارآمد انرژی را نشان می دهد که عملکرد بالا را با کاهش مصرف انرژی ترکیب می کند.LVPECL ریشه در توسعه تاریخی منطق همراه با امیتر (ECL) ، مزایای مشخصی را در برنامه های پر سرعت ، از جمله ارتباطات از راه دور و محاسبات ، که در آن راندمان انرژی و یکپارچگی سیگنال جدی است ، ارائه می دهد.این مقاله به ویژگی ها ، مزایا و ملاحظات طراحی LVPECL می پردازد و نقش تحول آمیز آن را در الکترونیک مدرن نشان می دهد.از کاربردهای عملی گرفته تا تمایزهای فنی ، کشف کنید که چگونه LVPECL آینده سیستم های دیجیتال را شکل می دهد.

کاتالوگ

طبقه بندی ECL

|

نوع |

VCC |

وهمی |

|

قصبه |

5.0 ولت |

0.0 ولت |

|

LVPECL |

3.3 ولت |

0.0 ولت |

|

2.5 ولت |

2.5 ولت |

0.0 ولت |

|

2.5 ولت |

0.0 ولت |

-2.5 ولت |

|

LVNECL |

0.0 ولت |

-3.3 ولت |

|

شبکه |

0.0 ولت |

-5.0 ولت |

جوانب منطق ECL/PECL/LVPECL

• منطق ECL به دلیل امپدانس بسیار قابل ملاحظه تولید ، به طور کلی بین 6 تا 8 اهم در حال سقوط است.این ویژگی با امپدانس ورودی فوق العاده بالا همراه است که می تواند تقریباً بی نهایت تلقی شود.چنین خصوصیاتی ECL را با قابلیت های رانندگی چشمگیر توانمند می کند ، و این امکان را برای مدیریت خطوط انتقال با امپدانس های مشخصه از 50 تا 130 اهم و بدون عملکرد قابل توجه AC فراهم می کند.توانایی حفظ یکپارچگی سیگنال در مسافت های طولانی بیشتر در برنامه هایی مانند سیم کشی پشت پرده و کابل های گسترده ای انجام می شود ، جایی که حفظ کیفیت سیگنال حاکم است.

• انعطاف پذیری دستگاه های ECL برای نوسانات ولتاژ و دما یکی دیگر از ویژگی های قابل توجه است که آنها را از فناوری های TTL و CMOS متمایز می کند.این ثبات در محیط هایی با شرایط مختلف و اطمینان از عملکرد مداوم ، سودمند است.علاوه بر این ، ساعتهای تولید شده توسط درایورهای ساعت ECL همگام سازی برتر و SKEW به حداقل می رسند ، که برای انتقال داده های پر سرعت مفید است.دقت در زمان بندی به افزایش عملکرد کلی سیستم کمک می کند ، بیشتر در برنامه هایی که نیاز به محدودیت زمان بندی دقیق دارند.

• در مقایسه ECL با سایر روشهای سیگنالینگ ، تمایز روشنی در مورد پشتیبانی فرکانس ایجاد می شود.ECL می تواند فرکانس هایی را که بیش از 10 گیگاهرتز است ، کنترل کند ، در حالی که LVD ها به طور معمول در حدود 1.5 گیگاهرتز قرار دارند.این قابلیت ECL را به عنوان یک انتخاب عالی برای برنامه های پر سرعت قرار می دهد ، با سرعت عملیاتی از 5 گیگاهرتز فراتر می رود و تأخیرهایی که به طور مداوم تحت 1NS نگهداری می شوند.چنین معیارهای عملکردی ECL را به ویژه برای مدارهای یکپارچه کوچک و متوسط و سیستم های دیجیتالی با سرعت بسیار بالا مفید می کند ، جایی که هر نانو ثانیه اهمیت دارد.

• سازگاری ECL با طیف گسترده تری از امپدانس های خط انتقال یک مزیت قابل توجه را ارائه می دهد.بر خلاف LVD ها ، که به یک مقاومت خاص خاتمه 100 اهم برای حمایت از یکپارچگی سیگنال نیاز دارد ، سازگاری ECL با امپدانس های مختلف احتمال بازتاب سیگنال و عوارض مرتبط را کاهش می دهد.این انعطاف پذیری نه تنها ملاحظات طراحی را ساده تر می کند بلکه قابلیت اطمینان را در برنامه های متنوع تقویت می کند.ظرفیت عملکرد مؤثر در طیف وسیعی از امپدانس ها به شما این امکان را می دهد تا ECL را در انواع گسترده تری از سیستم ها ادغام کنید بدون اینکه خواسته های سختگیرانه ای که معمولاً با سایر فناوری ها مرتبط است.

منفی منطق ECL/PECL/LVPECL

در حالی که Emitter همراه Logic (ECL) دارای مزایای چشمگیر در برنامه های پر سرعت است ، همچنین دارای معایب قابل توجهی است که توجه را تضمین می کند.مسائل اصلی شامل افزایش مصرف برق ، تحمل محدود برای سر و صدا و آسیب پذیری در برابر تداخل خارجی است.نوسان منطقی در مدارهای ECL فقط به 0.8 ولت محدود می شود ، که با تحمل نویز DC صرفاً 200mV جفت می شود.این ویژگی تجارت را برجسته می کند که در آن قابلیت های استثنایی سرعت ECL با هزینه کارآیی انرژی و مقاومت در برابر اختلالات سر و صدا به وجود می آید.در سناریوهای واقعی ، این می تواند چالش هایی را ایجاد کند ، به ویژه در محیط هایی که مدیریت مصرف انرژی خطرناک است یا در جایی که حفظ یکپارچگی سیگنال از اهمیت بالایی برخوردار است.

برای منطق همراه با امیت مثبت (PECL) ، بار خروجی استاندارد در 50 اهم با ولتاژ عرضه VCC-2V تنظیم شده است.تحت این پارامترها ، سطح استاتیک معمولی برای OUT+ و OUT- VCC-1.3V ، با جریان خروجی 14mA است.اگرچه این پیکربندی برای برخی از برنامه های کاربردی مؤثر است ، اما ممکن است به خوبی با همه شرایط مطابقت نداشته باشد ، به خصوص هنگام در نظر گرفتن پیچیدگی های مدیریت حرارتی و پیامدهای اتلاف قدرت مرتبط با این سطح خروجی.

ساختار مدار خروجی PECL

ورودی PECL یک جفت دیفرانسیل با امپدانس ورودی بالا است.برای دستیابی به حداکثر سطح سیگنال ورودی پویا ، ولتاژ حالت مشترک این جفت دیفرانسیل باید نسبت به VCC - 1.3V - مغرضانه باشد.برخی از تراشه ها شامل یک مدار تعصب یکپارچه هستند که امکان اتصال مستقیم بدون اجزای اضافی را فراهم می کند.با این حال ، برای تراشه های بدون این مدار تعصب داخلی ، یک تعصب DC خارجی باید در حین استفاده اعمال شود.

ساختار مدار ورودی PECL

سطح منطقی سطح PECL

|

پارامتر |

وضعیت |

حداقل |

معمولی |

حداکثر |

واحد |

|

خروجی زیاد |

TA = 0 ° C ~ 85 ° C |

VCC - 1.025 |

جدید |

VCC - 0.88 |

حرفهای |

|

TA = 40 درجه سانتیگراد |

VCC - 1.085 |

جدید |

VCC - 0.88 |

حرفهای |

|

|

تولید کم |

TA = 0 ° C ~ 85 ° C |

VCC - 1.81 |

جدید |

VCC - 1.62 |

حرفهای |

|

TA = 40 درجه سانتیگراد |

VCC - 1.83 |

جدید |

VCC - 1.55 |

حرفهای |

|

|

ورودی زیاد |

جدید |

VCC - 1.16 |

جدید |

VCC - 0.88 |

حرفهای |

|

ورودی کم |

جدید |

VCC - 1.81 |

جدید |

VCC - 1.48 |

حرفهای |

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

4N25 Optocoupler: ویژگی ها ، pinout و معادل ها

در 2024/12/27

ترانزیستور D882 توضیح داد: Pinout ، پیکربندی و نکات استفاده ایمن

در 2024/12/27

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147764

-

pinout uSB-C و ویژگی های

در 2000/04/18 111987

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111351

-

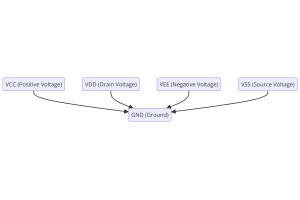

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83751

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79542

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66949

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63089

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63028

-

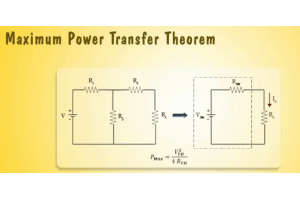

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54092

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52172