نمای کلی LFEC3E-3Q208C FPGA: ویژگی ها ، برنامه ها ، برنامه نویسی و مشخصات

در این مقاله ، شما در مورد LFEC3E-3Q208C ، FPGA از نیمه هادی شبکه Lattice خواهید آموخت.خواهید دید که این چیست ، ویژگی های اصلی ارائه شده و چرا برای بسیاری از طرح های میان رده مفید است.این محتوا همچنین شما را از طریق مشخصات ، برنامه های کاربردی و فرآیند برنامه نویسی گام به گام به همراه جوانب مثبت ، منفی و جزئیات تولید کننده آن به شما می رساند.کاتالوگ

LFEC3E-3Q208C چیست؟

در LFEC3E-3Q208C یک آرایه دروازه قابل برنامه ریزی با مقرون به صرفه (FPGA) از نیمه هادی مشبک است که به عنوان بخشی از خانواده Latticeec (اقتصاد) طراحی شده است.این خانواده برای ارائه راه حل های منطقی قابل برنامه ریزی که تعادل با عملکرد قابل اعتماد برای طرح های اصلی را تعادل می بخشد ، تهیه شده است.در سلسله مراتب Latticeec ، در رده میان رده قرار دارد و حدود 3000 عنصر منطقی و استفاده از انرژی کارآمد را ارائه می دهد و شکاف بین دستگاه های ورودی کوچکتر و مدلهای بزرگتر و پر منابع را ایجاد می کند.سری شبکه های مشبک/EC گسترده تر بر برنامه نویسی کم هزینه ، مقیاس پذیری و انعطاف پذیری در اندازه های مختلف دستگاه تأکید می کند ، با این که نوع EC بر عملکرد اقتصاد محور است.

به دنبال LFEC3E-3Q208C هستید؟برای بررسی سهام فعلی ، زمان سرب و قیمت گذاری با ما تماس بگیرید.

ویژگی های LFEC3E-3Q208C

• منابع منطقی

این دستگاه حدود 3،100 عنصر منطق را که در 384 بلوک سازماندهی شده اند ، ادغام می کند و ظرفیت کافی برای طرح های میان رده را فراهم می کند.این تعادل منابع باعث می شود که آن را برای منطق کنترل ، پردازش سیگنال و برنامه های تعبیه شده بدون هزینه بیش از حد مناسب کند.

• I/O قابل برنامه ریزی

با حداکثر 145 پین ورودی/خروجی قابل برنامه ریزی ، از طیف گسترده ای از گزینه های اتصال پشتیبانی می کند.این I/OS با استانداردهای مختلفی مانند LVCMOS ، LVTTL ، LVDS ، PCI و SSTL سازگار هستند و ادغام سیستم انعطاف پذیر را فعال می کنند.

• حافظه تعبیه شده

FPGA شامل RAM بلوک اختصاصی (EBR) و منابع RAM توزیع شده است که ذخیره سازی کارآمد روی تراشه را فراهم می کند.این امر به اجرای بافر داده ها ، جداول جستجو یا خاطرات تعبیه شده کوچک به طور مستقیم در داخل دستگاه اجازه می دهد.

• مدیریت ساعت

این ویژگی حداکثر چهار PLL یکپارچه است که ضرب فرکانس ، تقسیم و تغییر فاز را ارائه می دهد.این امر کنترل زمان بندی دقیق و هماهنگ سازی را برای طرح های پر سرعت امکان پذیر می کند.

• پشتیبانی حافظه DDR

این دستگاه شامل پشتیبانی سخت افزاری برای رابط های DDR ، قادر به اجرای DDR400 (200 مگاهرتز) است.این امر برای طرح هایی که نیاز به دسترسی به حافظه با سرعت بالا خارجی دارند ، عملی می شود.

• بازده قدرت

FPGA که با منبع اصلی 1.2 ولت کار می کند ، مصرف انرژی کلی سیستم را به حداقل می رساند.طراحی کم مصرف آن برای برنامه های قابل حمل یا حساس به انرژی ایده آل است.

• ویژگی های سطح سیستم

توابع داخلی مانند اسکن مرزی IEEE 1149.1 ، تجزیه و تحلیل منطق روی تراشه (ISPTRACY) و یک رابط فلش بوت SPI ، آزمایش و اشکال زدایی را ساده می کند.این ویژگی ها باعث کاهش زمان توسعه و بهبود قابلیت اطمینان طراحی می شود.

• پشتیبانی توسعه

این دستگاه با پشتیبانی از مجموعه طراحی ISPLEVER ، از سنتز خودکار ، مکان و مسیر و ابزارهای تأیید استفاده می کند.همچنین می توانید از بلوک های IP Isplevercore برای تسریع در عملکردهای مشترک و کوتاه کردن زمان به بازار استفاده کنید.

نمودار بلوک خانوادگی LatticeECP/EC

نمودار بلوک خانواده LatticeECP/EC (از جمله LFEC3E-3Q208C) نشان می دهد که چگونه FPGA ساخته شده است و چگونه قطعات آن با هم کار می کنند.سلولهای I/O قابل برنامه ریزی (PIC) در اطراف لبه ها قرار می گیرند تا تراشه را با دستگاه های خارجی وصل کنند و از بسیاری از استانداردهای سیگنال پشتیبانی کنند.در داخل ، واحدهای کاربردی قابل برنامه ریزی (PFU) عملیات منطقی را انجام می دهند ، با برخی از زوج ها به RAM بلوک تعبیه شده (EBR) برای ذخیره داده ها و برخی دیگر فقط روی منطق متمرکز شده اند.Sysclock PLLS سیگنال های ساعت را مدیریت می کند تا طراحی با سرعت و زمان مناسب اجرا شود.پورت SysConfig و درگاه JTAG به شما امکان می دهد FPGA را به راحتی برنامه ، آزمایش و اشکال زدایی کنید.این طرح به انعطاف پذیری LFEC3E-3Q208C ، عملکرد قابل اعتماد و ادغام ساده در طرح های حساس به هزینه می دهد.

نمودار برش LatticeECP/EC

برش موجود در خانواده LatticeECP/EC ، مانند LFEC3E-3Q208C ، واحد منطق اصلی است که LUT4 و بلوک های حمل را برای انجام منطق و عملیات حسابی ترکیب می کند.هر برش همچنین شامل Flip-Flops/Latches برای ذخیره داده ها و فعال کردن منطق پی در پی ، با چند برابر کننده ها برای مسیریابی سیگنال ها به صورت انعطاف پذیر یا از طریق رجیسترها یا مستقیم.این ساختار مهم است زیرا سرعت ، انعطاف پذیری و کارآیی FPGA را برای رسیدگی به طرح های دیجیتالی ساده و پیچیده به FPGA می دهد.در جدول زیر توضیحات سیگنال برش ، از جمله عملکرد ، انواع ، نام سیگنال ها و اهداف آنها خلاصه شده است.

|

عمل |

نوع |

نامهای سیگنال |

شرح |

|

ورودی |

سیگنال داده ها |

A0 ، B0 ، C0 ، D0 |

ورودی به LUT4 |

|

ورودی |

سیگنال داده ها |

A1 ، B1 ، C1 ، D1 |

ورودی به LUT4 |

|

ورودی |

چند منظوره |

m0 |

ورودی چند منظوره |

|

ورودی |

چند منظوره |

m1 |

ورودی چند منظوره |

|

ورودی |

سیگنال کنترل |

در نظر گرفتن |

فعال کردن ساعت |

|

ورودی |

سیگنال کنترل |

LSR |

مجموعه/تنظیم مجدد محلی |

|

ورودی |

سیگنال کنترل |

کلوچه |

ساعت سیستم |

|

ورودی |

سیگنال بین PFU |

فسین |

حمل سریع در |

|

خروجی |

سیگنال های داده |

F0 ، F1 |

ثبت نام خروجی LUT4 سیگنال های بای پس |

|

خروجی |

سیگنال های داده |

Q0 ، Q1 |

ثبت خروجی ها |

|

خروجی |

سیگنال های داده |

OFX0 |

خروجی یک Mux Lut5 |

|

خروجی |

سیگنال های داده |

OFX1 |

خروجی یک LUT6 ، LUT7 ، LUT8 2 MUX بسته به برش |

|

خروجی |

سیگنال بین PFU |

FCO |

برای مناسب ترین PFU خروجی زنجیره حمل سریع |

مشخصات LFEC3E-3Q208C

|

نوع |

پارامتر |

|

سازنده |

نیمه هادی مشبک |

|

ولتاژ - عرضه |

1.14V ~ 1.26V |

|

کل بیت های قوچ |

56،320 |

|

بسته دستگاه تأمین کننده |

208-pqfp (28x28) |

|

سری |

EC |

|

بسته / مورد |

208-bfqfp |

|

بسته بندی کردن |

سینی |

|

دمای عملیاتی |

0 درجه سانتیگراد 85 درجه سانتیگراد (TJ) |

|

تعداد عناصر/سلول های منطقی |

3،100 |

|

تعداد I/O |

145 |

|

نوع نصب |

سطح سطح |

|

شماره محصول پایه |

LFEC3 |

برنامه های LFEC3E-3Q208C

1. سیستم های کنترل تعبیه شده

LFEC3E-3Q208C برای کنترل کننده های تعبیه شده در دستگاه ها ، اتوماسیون صنعتی و دروازه IoT مناسب است.چگالی منطق متوسط آن و طراحی کم هزینه اجازه می دهد منطق عملکرد ثابت را با انعطاف پذیری قابل برنامه ریزی جایگزین کند.این امر به روزرسانی سیستم ها یا سازگاری با استانداردهای در حال تحول بدون طراحی مجدد سخت افزار آسانتر می شود.

2. رابط حافظه DDR

با پشتیبانی داخلی از حافظه DDR400 ، دستگاه می تواند بافر داده ، ورود به سیستم یا ذخیره موقت در برنامه ها را مدیریت کند.این ویژگی در سیستمهایی مفید است که سرعت حافظه خارجی مهم است اما عملکرد FPGA با کیفیت بالا لازم نیست.بسیاری از تعادل سرعت ، هزینه و راندمان حافظه بهره مند می شوند.

3. I/O Bridging و تبدیل پروتکل

با تشکر از پشتیبانی گسترده آن از استانداردهای I/O مانند LVCMOS ، LVTTL ، LVDS ، PCI و SSTL ، FPGA در پل زدن رابط های دیجیتال مختلف مؤثر است.این می تواند برای ترجمه سیگنال ها بین زیر سیستم ها پیکربندی شود ، و آن را در طرح های فناوری مختلط ارزشمند می کند.این انعطاف پذیری با فعال کردن سازگاری با اجزای جدید به افزایش عمر سخت افزار موجود کمک می کند.

4. برنامه های صنعتی و زیرساختی

این دستگاه همچنین می تواند در تجهیزات صنعتی و زیرساختی حساس به هزینه باشد که در آن قابلیت اطمینان و عملکرد متوسط کافی است.پشتیبانی آن از اسکن مرزی ، اشکال زدایی روی تراشه و عملکرد کم مصرف ، آن را برای سیستم هایی که خواستار بهره وری و نگهداری آسان هستند ، ایده آل می کند.نقش های معمولی شامل واحدهای کنترل ، ماژول های رابط و سیستم های نظارت است.

قطعات مشابه LFEC3E-3Q208C

|

مشخصات |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

عناصر منطقی (LUTS) |

3.1k پوند |

3.1k پوند |

3.1k پوند |

3.1k پوند |

1.5k پوند |

6.1k پوند |

|

بلوک های منطقی |

384 |

384 |

384 |

384 |

192 |

768 |

|

RAM بلوک تعبیه شده (EBR) |

55 کیلوبایت پوند |

55 کیلوبایت پوند |

55 کیلوبایت پوند |

55 کیلوبایت پوند |

18 کیلوبایت پوند |

92 کیلوبایت پوند |

|

فرکانس عملیاتی حداکثر |

340 مگاهرتز |

340 مگاهرتز |

340 مگاهرتز |

340 مگاهرتز |

300 مگاهرتز |

340 مگاهرتز |

|

I/O تعداد |

145 |

145 |

145 |

145 |

112 |

145 |

|

بسته بندی کردن |

208 pqfp |

208 pqfp |

208 pqfp |

208 pqfp |

208 pqfp |

208 pqfp |

|

ولتاژ اصلی |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

|

دامنه دما |

0 درجه سانتیگراد تا +70 درجه سانتیگراد |

-40 درجه سانتیگراد تا +85 درجه سانتیگراد |

0 درجه سانتیگراد تا +70 درجه سانتیگراد |

0 درجه سانتیگراد تا +70 درجه سانتیگراد |

0 درجه سانتیگراد تا +70 درجه سانتیگراد |

0 درجه سانتیگراد تا +70 درجه سانتیگراد |

|

نوع انطباق / بسته بندی |

استاندارد |

صنعتی |

بدون سرب (QN) |

نوع (Q) |

استاندارد |

استاندارد |

|

کاربرد |

چگالی میانی ، عمومی |

همان LFEC3E اما استفاده صنعتی |

همان LFEC3E اما مطابق با بسته بندی |

همان خانواده ، مهاجرت آسان |

گزینه هزینه کم چگالی |

بروزرسانی با چگالی بالاتر |

مراحل برنامه نویسی LFEC3E-3Q208C

قبل از شروع برنامه نویسی LFEC3E-3Q208C ، تهیه ابزارهای مناسب و درک جریان طراحی به پیکربندی دستگاه بسیار مهم است.هر مرحله بر روی مورد قبلی ساخته می شود ، بنابراین توجه دقیق یک روند برنامه نویسی صاف را تضمین می کند.

1. سخت افزار و نرم افزار برنامه نویسی را آماده کنید

شما با نصب برنامه نویس الماس Lattice یا سیستم ISPVM ، که ابزارهای رسمی این FPGA هستند ، شروع می کنید.سپس کابل برنامه نویسی JTAG مانند HW-USBN-2B را تنظیم کرده و مطمئن شوید که درایورها به درستی نصب شده اند.این مرحله تضمین می کند که رایانه شما بدون خطاهای اتصال آماده ارتباط با دستگاه هدف باشد.

2. طراحی خود را در نرم افزار توسعه پیاده سازی کنید

در مرحله بعد ، یک پروژه جدید در Lattice Diamond ایجاد کنید و LFEC3E-3Q208C را به عنوان دستگاه هدف خود انتخاب کنید.سپس پرونده های منبع Verilog یا VHDL خود را اضافه می کنید ، تکالیف پین را اعمال می کنید و هرگونه محدودیت زمان بندی را تعریف می کنید.پس از اتمام این کار ، شما طراحی را سنتز می کنید ، مکان و مسیر را انجام می دهید و در نهایت پرونده bitstream (.bit یا .jed) را تولید می کنید که برای برنامه نویسی استفاده می شود.

3 تخته و اتصالات را تنظیم کنید

اکنون ، کابل JTAG را به صفحه FPGA خود وصل کنید ، و مطمئن شوید که اتصال زمین قبل از اتصال خطوط سیگنال ایمن است.تأیید کنید که مقاومت های کشش و کشویی به درستی در جای خود قرار دارند ، به خصوص در خطوط TCK و تخلیه باز.اگر هیئت مدیره شما دارای پین های کنترل اضافی مانند Erase یا ISPEN است ، برای جلوگیری از تنظیم مجدد تصادفی در هنگام برنامه نویسی ، باید آنها را به درستی پیکربندی کنید.

4. دستگاه را برنامه ریزی کنید

با آماده سازی سخت افزار ، ابزار برنامه نویسی را راه اندازی کرده و کابل متصل خود را انتخاب کنید.پرونده Bitstream تولید شده را بارگیری کرده و بسته به تنظیم خود ، حالت مناسب را معمولاً JTAG انتخاب کنید.فرآیند برنامه نویسی را شروع کنید و این ابزار ضمن تأیید اینکه داده ها به درستی نوشته شده است ، FPGA را پیکربندی می کند.

5. پیکربندی را تأیید و اشکال زدایی کنید

پس از برنامه نویسی ، برای تأیید پیکربندی FPGA با موفقیت ، پین های انجام شده یا init را روی صفحه خود بررسی کنید.در صورت لزوم ، از آنالایزر منطق isptracy یا ویژگی های اسکن مرزی برای آزمایش عملکرد و اعتبارسنجی رفتار سیگنال استفاده کنید.شما می توانید هر زمان که نیاز به تغییر باشد ، چرخه طراحی و برنامه نویسی را تکرار کنید ، اطمینان حاصل کنید که پروژه شما گام به گام تصفیه شده است.

مزایا و معایب LFEC3E-3Q208C

مزایا

• مصرف کم مصرف ، مناسب برای طرح های حساس به انرژی

• مقرون به صرفه در مقایسه با FPGA های سطح بالاتر

• ابزار ساده با منحنی یادگیری آسان تر

• برای به روزرسانی پس از استقرار ، زمینه قابل تنظیم برای به روزرسانی

• بسته جمع و جور با تعادل خوب منابع

معایب

• عملکرد محدود در مقایسه با FPGA های بزرگتر

• منطق و ظرفیت حافظه پایین تر از دستگاه های سطح بالا

• کمتر هسته IP شخص ثالث و پشتیبانی اکوسیستم

•چین ابزار فاقد ویژگی های پیشرفته فروشندگان اصلی است

• برای رابط های با سرعت بسیار بالا مناسب نیست

ابعاد بسته بندی LFEC3E-3Q208C

|

نوع |

پارامتر |

|

نوع بسته بندی |

208-pqfp (بسته پلاستیکی چهار مسطح) |

|

اندازه بدن |

28 میلی متر × 28 میلی متر |

|

زمین |

0.5 میلی متر |

|

ارتفاع بسته (حداکثر) |

3.4 میلی متر پوند |

|

شمارش سرب |

208 پین |

|

سبک بسته بندی |

Gull-Wing Leads (چهار) |

|

نوع نصب |

سطح سطح |

|

رمز پرونده |

BFQFP-208 |

|

بسته بندی |

سینی |

تولید کننده LFEC3E-3Q208C

LFEC3E-3Q208C توسط تولید می شود شرکت نیمه هادی شبکه ، یک شرکت مستقر در ایالات متحده که مقر آن در هیلزبورو ، اورگان است.Lattice که در سال 1983 تأسیس شد ، در توسعه آرایه های دروازه با قدرت پایین ، مقرون به صرفه (FPGA) و راه حل های مرتبط تخصص دارد.این شرکت بر فعال کردن برنامه های کاربردی در ارتباطات ، محاسبات ، الکترونیک مصرفی ، صنعتی و خودرو تمرکز دارد.Lattice که به دلیل نوآوری در دستگاه های قابل برنامه ریزی با کارآیی انرژی شناخته شده است ، خود را به عنوان یک بازیگر اصلی در صنعت FPGA ، به ویژه برای طرح هایی که خواستار عوامل شکل جمع و جور ، کاهش مصرف انرژی و قابلیت اطمینان بالا هستند ، ایجاد کرده است.

پایان

LFEC3E-3Q208C ترکیبی خوب از کم هزینه ، استفاده کم مصرف و منطق و حافظه کافی را برای پروژه های میان رده ارائه می دهد.این برنامه از بسیاری از استانداردهای I/O پشتیبانی می کند ، دارای RAM و PLL داخلی است و می تواند با حافظه DDR400 کار کند و آن را برای کنترل ، رابط و کارهای صنعتی مفید کند.برنامه نویسی با ابزارهای مشبک ساده است و ویژگی های اشکال زدایی اضافی در آزمایش کمک می کند.اگرچه نمی تواند با سرعت و ظرفیت FPGA های بزرگتر مطابقت داشته باشد ، این یک انتخاب قابل اعتماد برای طرح هایی است که نیاز به انعطاف پذیری ، کارآیی و عملکرد مقرون به صرفه دارند.

برگه داده PDF

برگه های LFEC3E-3Q208C:

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

سوالات متداول [FAQ]

1. آیا LFEC3E-3Q208C از رابط های پر سرعت مانند PCIE یا Gigabit Ethernet پشتیبانی می کند؟

خیر. LFEC3E-3Q208C برای برنامه های اصلی و حساس به هزینه طراحی شده است ، بنابراین شامل فرستنده های سریال با سرعت بالا بومی نمی شود.در عوض بر روی رابط های موازی و پشتیبانی حافظه DDR تمرکز دارد.

آیا می توان LFEC3E-3Q208C را پس از استقرار دوباره برنامه ریزی کرد؟

بلهبه عنوان یک FPGA ، LFEC3E-3Q208C کاملاً قابل تنظیم است و امکان به روزرسانی ها و اصلاحات طراحی را حتی پس از استقرار فراهم می کند.این انعطاف پذیری هزینه های نگهداری طولانی مدت را کاهش داده و چرخه عمر محصول را گسترش می دهد.

3. چگونه LFEC3E-3Q208C با اشکال زدایی و آزمایش برخورد می کند؟

این دستگاه اسکن مرزی (IEEE 1149.1) ، تجزیه و تحلیل منطق روی تراشه (ISPTRACY) و پشتیبانی فلاش بوت SPI را ادغام می کند.این ابزارهای داخلی اشکال زدایی را ساده می کنند و نیاز به سخت افزار آزمایش خارجی را کاهش می دهند.

آیا LFEC3E-3Q208C می تواند طول عمر سیستم های سخت افزاری قدیمی را افزایش دهد؟

بله ، به لطف سازگاری گسترده I/O و قابلیت های پلنگ پروتکل ، می تواند سیستم های قدیمی تر را با اجزای جدیدتر رابط کند و به مشاغل کمک می کند تا سودمندی سخت افزار موجود را گسترش دهند.

5. چه ابزارهای برنامه نویسی برای LFEC3E-3Q208C لازم است؟

این برنامه با استفاده از برنامه نویس الماس Lattice یا سیستم ISPVM برنامه ریزی شده است.این ابزارها از ورودی طراحی ، تولید بیت استریم و پیکربندی دستگاه پشتیبانی می کنند و گردش کار را ساده تر می کنند.

AD73311LARS: برگه داده ، ویژگی ها ، راهنمای Pinout و برنامه نویسی

در 2025/08/28

نمای کلی CPLD EPM1270F256C4N MAX II: ویژگی ها ، مشخصات و برنامه ها

در 2025/08/28

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/19 147781

-

pinout uSB-C و ویژگی های

در 2000/04/19 112056

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/19 111352

-

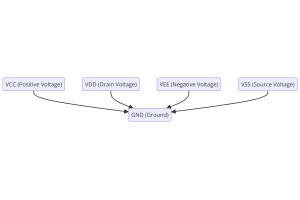

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/19 83810

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79622

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66992

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63118

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63055

-

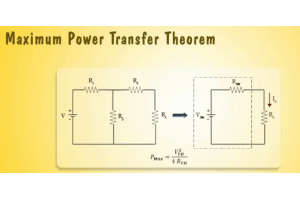

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54097

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52205