EP2S60F672C4 FPGA: ویژگی ها ، برنامه ها ، برنامه نویسی و راهنمای برگه داده

در این راهنما ، یک نمای کلی از EP2S60F672C4 ، یک FPGA قدرتمند از خانواده Intel Stratix II دریافت خواهید کرد.شما در مورد ویژگی های اصلی آن ، معماری ، ساختار بلوک و مشخصات فنی آن خواهید آموخت تا درک کنید که چگونه در طرح های دیجیتالی پیشرفته قرار می گیرد.همچنین شما را از طریق مراحل برنامه نویسی ، برنامه ها ، مزایا و مضرات خود طی می کند تا بتوانید دقیقاً از کجا و چگونه می توان از این دستگاه استفاده کرد.کاتالوگ

EP2S60F672C4 چیست؟

در EP2S60F672C4 یک FPGA با چگالی بالا از اینتل (قبلاً Altera) است که متعلق به خانواده Stratix II است.ساخته شده بر روی یک فرآیند SRAM 90 نانومتر ، 1.2 ولت ، ظرفیت منطقی قابل توجهی را در یک بسته FBGA 672 توپ ارائه می دهد و آن را برای سیستم های دیجیتالی پیچیده ایده آل می کند.به عنوان بخشی از سری EP2S ، دستگاه "60" در محدوده میانی تا بالا از ترکیب Stratix II قرار دارد و تعادل قوی چگالی منطق ، حافظه تعبیه شده و منابع I/O را ارائه می دهد.این FPGA که به دلیل معماری و قابلیت اطمینان قوی خود شناخته شده است ، در بسیاری از طرح های پیشرفته یک انتخاب قابل اعتماد است.

به دنبال EP2S60F672C4 هستید؟برای بررسی سهام فعلی ، زمان سرب و قیمت گذاری با ما تماس بگیرید.

مدل های CAD EP2S60F672C4

نماد EP2S60F672C4

ردپای EP2S60F672C4

مدل 3D EP2S60F672C4

ویژگی های EP2S60F672C4

• روند پیشرفته 90 نانومتر ، 1.2 ولت CMOS

EP2S60F672C4 بر روی یک فرآیند CMOS مس 90 نانومتر که با یک ولتاژ هسته 1.2 ولت کار می کند ، ساخته شده است.این فناوری باعث می شود سرعت بالا ، کاهش مصرف برق و چگالی منطق بیشتر در مقایسه با نسل های قدیمی تر FPGA.

• معماری ماژول منطق سازگار (ALM)

این دستگاه به جای عناصر منطقی سنتی از ALM به عنوان بلوک ساختاری منطق خود استفاده می کند.این معماری باعث بهبود استفاده از منابع می شود و باعث می شود توابع منطق پیچیده تری به طور مؤثر در همان منطقه سیلیکون اجرا شوند.

• تراکم منطق بالا

FPGA با تقریباً 60،440 عنصر منطقی (24176 ALM) ، از طرح های دیجیتالی بزرگ و پیشرفته پشتیبانی می کند.این ظرفیت بالا آن را برای برنامه هایی مانند پردازش سیگنال ، ارتباطات و سیستم های کنترل تعبیه شده مناسب می کند.

• Trimatrix ™ حافظه روی تراشه

EP2S60F672C4 سه نوع بلوک RAM ، (M512 ، M4K و M-RAM) را یکپارچه می کند تا در مجموع حدود 2.4 مگابایت حافظه تعبیه شده را فراهم کند.این ترکیب اجازه می دهد تا FIFO های کوچک ، بافرهای متوسط و خاطرات بزرگ پورت دوگانه را به طور موثر پیاده سازی کنید.

• بلوک های اختصاصی DSP

این دستگاه شامل 36 بلوک اختصاصی DSP است که برای عملیات حسابی مانند ضرب ، تجمع و فیلتر FIR طراحی شده است.این بلوک ها ضمن صرفه جویی در منابع منطق کلی ، عملکرد را در کارهای محاسباتی تقویت می کنند.

• یکپارچگی I/O با سرعت بالا و سیگنال

این استاندارد از استانداردهای مختلف I/O تک انتهایی و دیفرانسیل به همراه مدار تراز فاز پویا (DPA) پشتیبانی می کند.این ویژگی ها انتقال داده های پایدار و پر سرعت را تا 1 گیگابیت بر ثانیه امکان پذیر می کنند و از ارتباط قابل اعتماد با اجزای خارجی اطمینان می دهند.

• پشتیبانی از رابط حافظه خارجی غنی

FPGA با DDR ، DDR2 ، QDR II ، RLDRAM II و سایر استانداردهای حافظه سازگار است.پشتیبانی از رابط داخلی ، طراحی صفحه را ساده می کند و به توان داده های بالا برای برنامه های پرقدرت حافظه می رسد.

• مدیریت ساعت انعطاف پذیر

حداکثر 12 PLL روی تراشه اجازه می دهد تا سرعت ، تقسیم ، تغییر فاز و تعویض بدون گلاچ.شما می توانید دامنه های ساعت را به خوبی تنظیم کرده و لرزش را کاهش دهید و از فرکانس های ساعت داخلی تا 500-550 مگاهرتز پشتیبانی کنید.

• رمزگذاری و تنظیم مجدد bitstream

EP2S60F672C4 از رمزگذاری Bitstream مبتنی بر AES برای تأمین مالکیت معنوی پشتیبانی می کند.همچنین قابلیت تنظیم مجدد از راه دور را ارائه می دهد و به روزرسانی های درون میدانی را بدون تعویض دستگاه امکان پذیر می کند.

نمودار بلوک Stratix II

نمودار بلوک Stratix II ، همانطور که برای EP2S60F672C4 نشان داده شده است ، ترتیب داخلی منابع منطق ، حافظه و DSP را نشان می دهد که هسته FPGA را تشکیل می دهند.بلوک های آرایه منطق (آزمایشگاه ها) در یک شبکه معمولی مرتب شده اند ، که توسط ستون های قوچ و DSP تعبیه شده احاطه شده است ، که قابلیت های سریع حسابی و ذخیره سازی روی تراشه را ارائه می دهند.عناصر I/O محیطی و شبکه های ساعت این ساختار را قاب می کنند و امکان انتقال کارآمد داده و کنترل زمان بندی بین FPGA و دستگاه های خارجی را فراهم می کنند.این نمودار مهم است زیرا به درک چگونگی سازماندهی بلوک های عملکردی مختلف کمک می کند و به آنها امکان می دهد تا قرارگیری ، مسیریابی و عملکرد کلی سیستم را بهینه کنند.

نمودار Banks Stratix II/O

این نمودار Banks Stratix II I/O نشان می دهد که چگونه پین های ورودی/خروجی EP2S60F672C4 گروه بندی می شوند و هر گروه از چه استانداردهای الکتریکی پشتیبانی می کند.هر بانک I/O به گونه ای طراحی شده است که سطح ولتاژ خاص ، انواع سیگنالینگ و کارکردهایی مانند LVTTL ، SSTL ، LVDS یا استانداردهای ورودی ساعت را کنترل کند.طرح نشان می دهد که چگونه بانک های مختلف (به عنوان مثال ، 1 ، 2 ، 5 ، 6 در مقابل 3 ، 4 ، 7 ، 8 ، و غیره) برای سیگنالینگ دیفرانسیل I/O با هدف کلی ، از جمله پشتیبانی از ورودی ساعت LVDS/LVPECL در لبه ها بهینه می شوند.درک این ساختار هنگام اختصاص پین مهم است ، زیرا انتخاب مناسب بانک سازگاری الکتریکی را تضمین می کند ، مسیریابی تخته را ساده می کند و عملکرد FPGA را در طرح های پر سرعت به حداکثر می رساند.

مشخصات EP2S60F672C4

|

نوع |

پارامتر |

|

سازنده |

Altera/Intel |

|

سری |

stratix® II |

|

بسته بندی |

سینی |

|

وضعیت جزئی |

منسوخ |

|

تعداد آزمایشگاه ها/CLBS |

3022 |

|

تعداد عناصر/سلول های منطقی |

60،440 |

|

کل بیت های قوچ |

2،544،192 |

|

تعداد I/O |

492 |

|

ولتاژ - عرضه |

1.15 V ~ 1.25 V |

|

نوع نصب |

سطح سطح |

|

دمای عملیاتی |

0 درجه سانتیگراد 85 درجه سانتیگراد (TJ) |

|

بسته / مورد |

672 BBGA |

|

بسته دستگاه تأمین کننده |

672-fbga (27 27 27) |

|

شماره محصول پایه |

EP2S60 |

برنامه های EP2S60F672C4

1. پردازش سیگنال دیجیتال (DSP) و فیلتر

EP2S60F672C4 برای اجرای توابع DSP با کارایی بالا مانند فیلترهای FIR و IIR ، پردازش FFT و عملیات پیچیده حسابی مناسب است.بلوک های DSP اختصاصی آن دارای ضرب و تجمع به طور کارآمد هستند و منابع منطقی کلی را برای سایر کارها آزاد می کنند.حافظه On-Chip Trimatrix to امکان بافر و لوله کشی داده های صاف را امکان پذیر می کند ، که برای پردازش در زمان واقعی با نرخ نمونه بالا بسیار عالی است.این باعث می شود دستگاه برای برنامه های پیشرفته صوتی ، فیلم و رادار ایده آل باشد.

ترتیب. ارتباطات و شبکه های پر سرعت

رابط های I/O با سرعت بالا FPGA و اتصال فاز پویا (DPA) از انتقال داده های قابل اعتماد و سطح گیگابیت پشتیبانی می کند.این می تواند پروتکل های ارتباطی و توابع لایه فیزیکی را برای سیستمهایی مانند روترها ، سوئیچ ها و اتصالات پشت صفحه اجرا کند.با ظرفیت منطقی بزرگ و PLL های انعطاف پذیر ، می تواند زمان بندی پیچیده و تبدیل پروتکل بین چندین رابط با سرعت بالا را مدیریت کند.این قابلیت ها آن را برای زیرساخت های مخابراتی و تجهیزات شبکه ای با پهنای باند بالا مناسب می کند.

3. کنترل کننده های حافظه و سیستم های پردازش داده

EP2S60F672C4 از رابط های مختلف حافظه خارجی از جمله DDR ، DDR2 ، RLDRAM II و QDR II پشتیبانی می کند و آن را برای طراحی کنترل کننده های حافظه باند بالا ایده آل می کند.این می تواند بافر داده ها ، تولید آدرس و داوری را با سرعت زیاد با حداقل تأخیر اداره کند.ترکیبی از شبکه های ساعت سریع و بلوک های قوچ تعبیه شده امکان مدیریت کارآمد جریان داده های بزرگ را فراهم می کند.این امر باعث می شود FPGA برای پردازش تصویر ، پخش ویدیو و سیستم عامل های محاسباتی علمی که به توان داده های سنگین متکی هستند ، مناسب باشد.

4. منطق سفارشی و شتاب جاسازی شده

FPGA با بیش از 60،000 عنصر منطقی و مدیریت ساعت غنی ، می تواند میزبان شتاب دهنده های سخت افزاری سفارشی برای الگوریتم های خاص باشد.طراحان غالباً از آن برای بارگیری کارهای محاسباتی فشرده از CPU ها ، مانند رمزگذاری ، تجزیه پروتکل یا حلقه های کنترل در زمان واقعی استفاده می کنند.همچنین می تواند چندین بلوک کاربردی را ادغام کند ، و آن را برای طرح های پیچیده SoC مناسب مناسب می کند.این انعطاف پذیری آن را در برنامه هایی مانند اتوماسیون صنعتی ، سیستم های امنیتی و واحدهای کنترل هوافضا ارزشمند می کند.

5. سیستم عامل های نمونه سازی و توسعه آموزشی

دستگاه EP2S60 معمولاً در کیت های توسعه FPGA که برای نمونه سازی ، آزمایش و تحقیقات دانشگاهی استفاده می شود ، یافت می شود.تعادل ظرفیت منطق آن ، تعداد I/O و قابلیت های DSP به مهندسین و دانشجویان این امکان را می دهد تا سیستم های کامل را در یک تراشه واحد پیاده سازی و تأیید کنند.این پشتیبانی از تکرار سریع طرح های دیجیتال پشتیبانی می کند و تأیید سخت افزار را قبل از ارتکاب به توسعه ASIC امکان پذیر می کند.بسیاری از دانشگاه ها و آزمایشگاه های تحقیق و توسعه از آن برای آموزش مفاهیم پیشرفته طراحی دیجیتال و پردازش سیگنال استفاده می کنند.

قسمتهای مشابه EP2S60F672C4

|

مشخصات |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672i4

|

EP2S60F672i3n |

|

خانواده / سریال |

طبقه دوم |

طبقه دوم |

طبقه دوم |

طبقه دوم |

طبقه دوم |

طبقه دوم |

|

عناصر منطقی (LE) |

60،440 |

60،440 |

60،440 |

60،440 |

60،440 |

60،440 |

|

صدقه |

24176 |

24176 |

24176 |

24176 |

24176 |

24176 |

|

بسته بندی کردن |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

درجه سرعت |

C4 (STD) |

C3 (سریعتر) |

C5 (سریعتر) |

C5 (سریعتر) |

I4 (STD) |

i3 (سریعتر) |

|

درجه درجه حرارت |

تجاری (70 درجه سانتیگراد 0) |

تجاری |

تجاری |

تجاری |

صنعتی (100 درجه سانتیگراد ~ 40 درجه سانتیگراد) |

صنعتی (100 درجه سانتیگراد ~ 40 درجه سانتیگراد) |

|

پین I/O |

492 |

492 |

492 |

492 |

492 |

492 |

|

حافظه روی تراشه |

2.4 مگابیت |

2.4 مگابیت |

2.4 مگابیت |

2.4 مگابیت |

2.4 مگابیت |

2.4 مگابیت |

|

ولتاژ اصلی |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

1.2 ولت |

|

تفاوت کلیدی |

سرعت تجاری پایه |

سطل سرعت C3 ، بدون سرب "N" |

سطل با سرعت بالاتر |

سطل با سرعت بالاتر ، نوع "n" |

دمای صنعتی ، تراکم مشابه |

صنعتی ، سرعت سریعتر ، بدون سرب |

مراحل برنامه نویسی EP2S60F672C4

قبل از اینکه بتوانید از EP2S60F672C4 FPGA در طراحی خود استفاده کنید ، باید آن را به درستی با Bitstream کامپایل شده خود پیکربندی کنید.این فرآیند شامل تهیه فایل برنامه نویسی ، تنظیم رابط سخت افزار و اطمینان از بارگذاری درست پیکربندی در برق است.

مرحله 1: طرح خود را ایجاد و کامپایل کنید

شما با توسعه طراحی منطق خود با استفاده از نرم افزار Intel Quartus II شروع می کنید.پس از اتمام طرح ، آن را برای تولید فایل برنامه نویسی (.sof یا .pof) به طور خاص برای دستگاه EP2S60F672C4 کامپایل می کنید.فرآیند تدوین زمان بندی ، تکالیف پین و استفاده از منابع را بررسی می کند تا اطمینان حاصل شود که طراحی شما در معماری FPGA قرار دارد.پس از گردآوری ، bitstream شما برای پیکربندی دستگاه آماده است.

مرحله 2: سخت افزار برنامه نویسی را تنظیم کنید

در مرحله بعد ، رابط برنامه نویسی فیزیکی بین رایانه شخصی و صفحه FPGA خود را آماده می کنید.به طور معمول ، این شامل اتصال یک کابل JTAG بلوستر یا سازگار به درگاه JTAG دستگاه است.شما باید تأیید کنید که کوارتوس II برنامه نویس را تشخیص می دهد و دستگاه هدف به درستی تشخیص داده می شود.این مرحله قبل از شروع فرآیند پیکربندی ، ارتباط پایدار را تضمین می کند.

مرحله 3: فایل برنامه نویسی را در دستگاه بارگذاری کنید

با استفاده از ابزار برنامه نویس کوارتوس II ، پرونده کامپایل شده .sof یا .pof را اضافه می کنید و EP2S60F672C4 را از لیست دستگاه شناسایی شده انتخاب می کنید.سپس دنباله برنامه نویسی را آغاز می کنید ، که در طی آن بیت استریم منتقل می شود و به سلولهای پیکربندی SRAM FPGA بارگیری می شود.برای تأیید پیکربندی موفقیت آمیز ، باید پیام های پیشرفت و وضعیت را کنترل کنید.پس از اتمام ، FPGA بلافاصله اجرای منطق برنامه ریزی شده را آغاز می کند.

مرحله 4: پیکربندی و عملکرد را تأیید کنید

پس از برنامه نویسی ، شما تأیید می کنید که دستگاه مطابق آنچه در نظر گرفته شده است ، کار می کند.کوارتوس II گزینه تأیید را برای بررسی سیگنال های پیکربندی CRC و وضعیت فراهم می کند ، و اطمینان حاصل می کند که طرح به درستی بارگذاری شده است.همچنین می توانید توابع I/O خود را آزمایش کنید یا یک شبیه سازی عملکردی را برای تأیید رفتار سیستم اجرا کنید.این مرحله آخر تضمین می کند که طراحی شما کاملاً عملیاتی و پایدار روی سخت افزار باشد.

مزایا و مضرات EP2S60F672C4

مزایا

• چگالی منطق بالا برای طرح های پیچیده

• نسبت عملکرد خوب به هزینه

• مهاجرت آسان در همان خانواده

• ابزارهای توسعه پایدار و بالغ

• قابلیت اطمینان اثبات شده در استفاده صنعتی

معایب

• منبع منسوخ و سخت تر است

• مصرف انرژی بالاتر از FPGA های جدیدتر

• هیچ گیرنده ای با سرعت بالا مدرن نیست

• بسته شدن زمان سخت تر در استفاده زیاد

• مقیاس پذیری محدود برای پروتکل های آینده

ابعاد بسته بندی EP2S60F672C4

|

نوع |

پارامتر |

|

نوع بسته بندی |

672-fbga (Fineline BGA) |

|

اندازه بدن (L × W) |

27.00 میلی متر × 27.00 میلی متر |

|

ارتفاع کل بسته (A) |

حداکثر 3.50 میلی متر |

|

ارتفاع ایستاده (A1) |

حداقل 0.30 میلی متر |

|

ضخامت بستر (A2) |

حداکثر 3.00 میلی متر |

|

قطر توپ (ب) |

0.50 میلی متر - 0.70 میلی متر |

|

زمین توپ (E) |

1.00 میلی متر |

|

تعداد توپ |

672 |

|

سبک نصب |

سطح سطح |

|

شرح بسته بندی |

FBGA ، 27 27 27 میلی متر شبکه |

تولید کننده EP2S60F672C4

FPGA EP2S60F672C4 توسط تولید می شود شرکت Altera، پیشگام پیشرو در دستگاه های منطقی قابل برنامه ریزی.در سال 2015 ، Altera توسط این کشورو این محصول اکنون تحت گروه راه حل های قابل برنامه ریزی اینتل (PSG) قرار دارد ، که همچنان به حمایت و تأمین خانواده های FPGA تأسیس شده Altera ادامه می دهد.اینتل خط Stratix II را به عنوان بخشی از نمونه کارها محصول میراث خود ، تضمین اسناد ، پشتیبانی از ابزار و در دسترس بودن طولانی مدت برای برنامه های صنعتی و ارتباطی حفظ می کند.

پایان

EP2S60F672C4 از چگالی منطق بالا ، معماری حافظه انعطاف پذیر و ویژگی های قوی I/O برای پشتیبانی از سیستم های دیجیتالی پیچیده استفاده می کند.طراحی مبتنی بر ALM ، حافظه trimatrix ™ ، بلوک های DSP و ویژگی های مدیریت ساعت امکان اجرای کارآمد برنامه های خواستار را فراهم می کند.در حالی که قابلیت اطمینان و پشتیبانی از توسعه بالغ را ارائه می دهد ، اما در مقایسه با نسل های جدیدتر FPGA با محدودیت هایی مانند منسوخ و عدم وجود گیرنده های مدرن روبرو است.به طور کلی ، عملکرد متعادل و تطبیق پذیری آن ، آن را به یک انتخاب محکم برای پردازش سیگنال ، ارتباطات ، کاربرد داده ها و برنامه های نمونه سازی تبدیل می کند.

برگه داده PDF

برگه داده های EP2S60F672C4:

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

سوالات متداول [FAQ]

1. آیا EP2S60F672C4 می تواند با رابط های حافظه مدرن DDR کار کند؟

بله ، از رابط های DDR ، DDR2 ، QDR II و RLDRAM II پشتیبانی می کند ، که بسیاری از استانداردهای حافظه خارجی مشترک را پوشش می دهد.این امر باعث می شود تا برنامه های پردازش داده های پهنای باند بالا مناسب باشد.

2. آیا EP2S60F672C4 نیاز به کار یا ذخیره سازی ویژه دارد؟

بله ، مانند سایر مؤلفه های بسته بندی شده BGA ، باید در بسته بندی های کنترل شده با رطوبت ذخیره شود و با ESD محافظت شود.پیروی از شیوه های ذخیره سازی مناسب به حفظ لحیم پذیری و قابلیت اطمینان دستگاه در حین مونتاژ کمک می کند.

3. چگونه می توانید مصرف برق را در طرح های EP2S60F672C4 کاهش دهید؟

شما می توانید استفاده از منطق ، ساعتهای بلااستفاده دروازه ، ولتاژ I/O را در صورت امکان بهینه کنید و گزینه های سنتز آگاهی از برق را در کوارتوس II به حداقل برسانید تا به حداقل برسد و به حداقل برسد.

4. چه ابزارهای برنامه نویسی برای EP2S60F672C4 مورد نیاز است؟

برای طراحی ، تدوین و برنامه نویسی به همراه یک کابل JTAG USB یا سازگار برای پیکربندی دستگاه ، به نرم افزار Intel Quartus II Intel نیاز دارید.

5. آیا EP2S60F672C4 از بروزرسانی های درون میدانی یا تنظیم مجدد از راه دور پشتیبانی می کند؟

بله ، از رمزگذاری BitStream مبتنی بر AES و پیکربندی از راه دور پشتیبانی می کند و به شما امکان می دهد سیستم خود را به طور ایمن به روز کنید بدون اینکه FPGA را جایگزین کنید.

همه چیز در مورد نیمه هادی شبکه LFXP6C-3FN256C

در 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT ، ویژگی ها ، برنامه نویسی و راهنمای برگه

در 2025/10/3

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/19 147781

-

pinout uSB-C و ویژگی های

در 2000/04/19 112056

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/19 111352

-

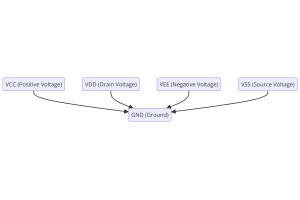

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/19 83810

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79622

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66992

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63118

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63055

-

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54097

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52205