EP1C4F400C8 FPGA: ویژگی ها ، مشخصات ، برنامه نویسی و گزینه های دیگر

اگر با منطق قابل برنامه ریزی کار می کنید ، EP1C4F400C8 یک تعادل عملی از عملکرد و هزینه را به شما می دهد.در این مقاله ، شما می آموزید که این FPGA چیست ، ویژگی های اصلی آن مانند ظرفیت منطقی ، حافظه و گزینه های I/O و چگونگی ساختار آن از طراحی قابل اعتماد پشتیبانی می کند.همچنین مشخصات ، برنامه های آن در سیستم ها ، فرآیند برنامه نویسی و نحوه مقایسه آن با قسمت های مشابه را مشاهده خواهید کرد.کاتالوگ

EP1C4F400C8 چیست؟

در EP1C4F400C8 عضو خانواده Cyclone FPGA اینتل (که قبلاً Altera بود) است ، به عنوان یک راه حل منطق قابل برنامه ریزی مقرون به صرفه و قابل اعتماد طراحی شده است.این دستگاه که بر روی یک فرآیند SRAM 0.13 میکرومتر ساخته شده است ، چگالی منطقی متوسط و گزینه های I/O انعطاف پذیر را در یک بسته جمع و جور FBGA-400 ارائه می دهد.خانواده سیکلون ، که شامل دستگاه هایی مانند EP1C3 ، EP1C6 ، EP1C12 و EP1C20 است ، برای تعادل عملکرد و قیمت مناسب برای طرح های مقیاس پذیر ایجاد شده است و امکان مهاجرت آسان بین سطح چگالی و بسته ها را فراهم می کند.معروف به ثبات و پذیرش گسترده ، این یک انتخاب قابل اعتماد در طرح های میراث است.

به دنبال EP1C4F400C8 هستید؟برای بررسی سهام فعلی ، زمان سرب و قیمت گذاری با ما تماس بگیرید.

مدل های CAD EP1C4F400C8

نماد EP1C4F400C8

ردپای EP1C4F400C8

مدل 3D EP1C4F400C8

ویژگی های EP1C4F400C8

• ظرفیت منطقی

EP1C4F400C8 حدود 4000 عنصر منطقی را ارائه می دهد ، که در 400 بلوک آرایه منطق (آزمایشگاه ها) سازماندهی شده اند.این امر باعث می شود تا ضمن حفظ راندمان هزینه ، برای طرح های میان رده ای که نیاز به چگالی منطق متوسط دارند ، مناسب باشد.

• حافظه تعبیه شده

این تقریباً 76.5 کیلوبیت حافظه تعبیه شده را ادغام می کند.این RAM داخلی از بافر ، ذخیره سازی و عملکردهای کوچک حافظه پشتیبانی می کند و نیاز به اجزای حافظه خارجی را در بسیاری از طرح ها کاهش می دهد.

• تعداد I/O زیاد

این دستگاه 301 پین I/O قابل تنظیم کاربر را در بسته 400 توپ FBGA خود فراهم می کند.این تعداد پین بالا اتصال غنی را برای سیستم های پیچیده ای که نیاز به چندین رابط محیطی دارند ، امکان پذیر می کند.

• پشتیبانی از استانداردهای گسترده I/O

این استاندارد از چندین استاندارد I/O از جمله LVTTL ، LVCMOS ، SSTL-2 ، SSTL-3 و LVD های دیفرانسیل پشتیبانی می کند.این انعطاف پذیری به FPGA اجازه می دهد تا مستقیماً با انواع خانواده های منطق مدرن و دستگاه های حافظه ارتباط برقرار کند.

• سیگنالینگ دیفرانسیل پر سرعت

با پشتیبانی LVDS حداکثر 640 مگابیت در ثانیه ، FPGA نیازهای انتقال سریع داده را کنترل می کند.این امر باعث می شود برنامه هایی مانند پیوندهای ارتباطی با سرعت بالا و رابط های دیجیتال سریع عملی شود.

• مدیریت ساعت با PLLS

تراشه دو حلقه قفل شده فاز (PLL) و هشت شبکه ساعت جهانی را ادغام می کند.این ویژگی ها امکان تولید دقیق ساعت ، ضرب و کنترل لرزش را برای برنامه های کاربردی مهم به زمان فراهم می کند.

• عملکرد هسته ولتاژ کم

دستگاه با ولتاژ هسته ای 1.5 ولت کار می کند ، دستگاه با مصرف انرژی کمتری عملکرد را متعادل می کند.این سطح ولتاژ برای فناوری CMOS 0.13 میکرومتر مورد استفاده در ساخت آن بهینه شد.

• ولتاژ I/O انعطاف پذیر

FPGA از ولتاژ I/O 1.5 ولت ، 1.8 ولت ، 2.5 ولت و 3.3 ولت در بانک های مختلف پشتیبانی می کند.این تطبیق پذیری آن را قادر می سازد تا با میراث و اجزای سیستم مدرن ارتباط برقرار کند.

• پیکربندی مبتنی بر SRAM

مانند سایر FPGA های سیکلون ، مبتنی بر SRAM است و در هر قدرت نیاز به تنظیم مجدد دارد.این انعطاف پذیری را برای به روزرسانی ها فراهم می کند ، اما همچنین یک دستگاه پیکربندی خارجی یا کنترل کننده را ضروری می کند.

• پشتیبانی از فشرده سازی bitstream

EP1C4F400C8 از بارگذاری بیت استرج فشرده شده در طول پیکربندی پشتیبانی می کند.این امر نیازهای حافظه خارجی را کاهش می دهد و زمان پیکربندی را سرعت می بخشد.

• انطباق PCI

این شامل پشتیبانی داخلی برای استانداردهای PCI (33/66 مگاهرتز ، 32/64 بیتی) است.این ویژگی به دستگاه اجازه می دهد تا مستقیماً در سیستم هایی که نیاز به رابط PCI دارند بدون منطق پل اضافی ادغام شود.

ساختار آزمایشگاه سیکلون

نمودار ساختار بلوک آرایه منطق (آزمایشگاه) مورد استفاده در FPGA های سیکلون مانند EP1C4F400C8 را نشان می دهد.هر آزمایشگاه به شبکه ای از اتصالات متصل می شود: اتصالات ردیف ، اتصالات ستون و اتصالات محلی که سیگنال ها بین عناصر منطقی و سایر بلوک ها مسیر دارند.اتصالات پیوند مستقیم مسیرهای سریع و کم تأخیر را به آزمایشگاههای مجاور ارائه می دهند و عملکرد زمان بندی را در مسیرهای سیگنال بهبود می بخشند.این معماری مهم است زیرا باعث افزایش انعطاف پذیری مسیریابی با راندمان می شود و FPGA را قادر می سازد تا ضمن بهینه سازی سرعت و منطقه ، طرح های پیچیده ای را انجام دهد.

نمودار بانکی I/O Cyclone

نمودار ساختار بانکی I/O FPGA های سیکلون مانند EP1C4F400C8 را نشان می دهد.این دستگاه به چهار بانک I/O تقسیم می شود که هر یک از اتوبوس عرضه خود را تأمین می کنند و این امکان را می دهد که استانداردهای مختلف ولتاژ را در یک FPGA واحد مخلوط کند.همه بانک ها طیف گسترده ای از استانداردهای I/O از جمله LVTTL ، LVCMOS ، LVDS ، RSDS و SSTL را پشتیبانی می کنند ، در حالی که بانک های 1 و 3 همچنین از PCI 3.3-V برای سازگاری با سیستم های میراث پشتیبانی می کنند.این معماری انعطاف پذیر I/O مهم است زیرا ادغام یکپارچه را با دستگاه ها و رابط های متنوع خارجی امکان پذیر می کند و FPGA را با برنامه های مختلف سازگار می کند.

مشخصات EP1C4F400C8

|

نوع |

پارامتر |

|

سازنده |

Altera/Intel |

|

سری |

سیکلون |

|

بسته بندی |

سینی |

|

وضعیت جزئی |

منسوخ |

|

تعداد آزمایشگاه ها/CLBS |

400 |

|

تعداد عناصر/سلول های منطقی |

4000 |

|

کل بیت های قوچ |

78،336 |

|

تعداد I/O |

301 |

|

ولتاژ - عرضه |

1.425V ~ 1.575V |

|

نوع نصب |

سطح سطح |

|

دمای عملیاتی |

0 درجه سانتیگراد 85 درجه سانتیگراد (TJ) |

|

بسته / مورد |

400 جفت |

|

بسته دستگاه تأمین کننده |

400-FBGA (21 21 21) |

|

شماره محصول پایه |

EP1C4 |

برنامه های EP1C4F400C8

1. پردازش سیگنال دیجیتال (DSP)

EP1C4F400C8 را می توان برای انجام کارهایی مانند فیلتر ، FFT و مدولاسیون سیگنال برنامه ریزی کرد.ترکیب آن از عناصر منطقی و حافظه تعبیه شده ، آن را برای پردازش با سرعت بالا مناسب می کند.این اجازه می دهد تا تراشه های سنتی DSP را با یک راه حل انعطاف پذیر FPGA جایگزین کند که می تواند برای الگوریتم های مختلف برنامه ریزی مجدد شود.

2. سیستم های تعبیه شده و کنترل

در سیستم های صنعتی و تعبیه شده ، این FPGA اغلب برای اجرای کنترل کننده های سفارشی ، ترتیب سنج ها و ماشین های دولتی استفاده می شود.منطق قابل تنظیم آن اجازه می دهد تا رفتار سخت افزاری را دقیقاً به نیازهای سیستم تنظیم کند.با ادغام منطق کنترل در FPGA ، تعداد اجزای خارجی کاهش می یابد ، قابلیت اطمینان و کاهش هزینه را بهبود می بخشد.

3.

دستگاه از چندین استاندارد I/O پشتیبانی می کند و می تواند به عنوان پلی بین پروتکل های مختلف ارتباطی عمل کند.این ماده اغلب برای اتصال PCI ، LVDS ، SDRAM و سایر رابط های یکپارچه در یک سیستم استفاده می شود.این امر باعث می شود در تجهیزات شبکه ، کنترل کننده های تعبیه شده و تبدیل رابط میراث به مدرن بسیار مفید باشد.

4. دستیابی و پردازش داده ها

با در دسترس بودن I/O بالا و حافظه انعطاف پذیر ، EP1C4F400C8 برای سیستم های جمع آوری داده ها مناسب است.این می تواند به طور مستقیم با ADC و سنسورها رابط کند ، داده ها را به موقع پردازش کرده و آن را برای ذخیره سازی یا انتقال آماده کند.چنین برنامه هایی در ابزارهای پزشکی ، تجهیزات آزمایش و دستگاه های اندازه گیری علمی متداول است.

قسمتهای مشابه EP1C4F400C8

|

مشخصات |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

سازنده |

altera (اینتل) |

altera (اینتل) |

altera (اینتل) |

altera (اینتل) |

altera (اینتل) |

altera (اینتل) |

|

خانواده FPGA |

سیکلون (EP1C4) |

سیکلون (EP1C4) |

سیکلون (EP1C4) |

سیکلون (EP1C4) |

سیکلون (EP1C4) |

سیکلون (EP1C4) |

|

عناصر منطقی (LES) |

4000 |

4000 |

4000 |

4000 |

4000 |

4000 |

|

حافظه جاسازی شده (بیت) |

76.5 kbits |

76.5 kbits |

76.5 kbits |

76.5 kbits |

76.5 kbits |

76.5 kbits |

|

پین I/O |

301 |

301 |

301 |

301 |

249 |

97 |

|

بسته / مورد |

400 fbga |

400 fbga |

400 fbga |

400 fbga |

324-fbga |

144-TQFP |

|

درجه سرعت |

C8 |

C8 |

C8 |

C6 (سریعتر) |

C8 |

C8 |

|

ولتاژ اصلی |

1.5 ولت |

1.5 ولت |

1.5 ولت |

1.5 ولت |

1.5 ولت |

1.5 ولت |

|

دمای عملیاتیدامنه |

0 درجه سانتیگراد 85 درجه سانتیگراد |

0 درجه سانتیگراد 85 درجه سانتیگراد |

0 درجه سانتیگراد 85 درجه سانتیگراد |

0 درجه سانتیگراد 85 درجه سانتیگراد |

0 درجه سانتیگراد 85 درجه سانتیگراد |

0 درجه سانتیگراد 85 درجه سانتیگراد

|

مراحل برنامه نویسی EP1C4F400C8

قبل از استفاده از EP1C4F400C8 FPGA ، باید طرح خود را در دستگاه بارگذاری کنید.برنامه نویسی شامل پیکربندی FPGA با یک فایل bitstream است ، بنابراین می داند چگونه به عنوان مدار مورد نظر خود رفتار کند.

1. طرح پیکربندی و تنظیم پین های MSEL را انتخاب کنید

شما با انتخاب طرح پیکربندی متناسب با تنظیم شما ، مانند سریال فعال ، سریال منفعل یا JTAG ، شروع می کنید.این کار با تنظیم پین های MSEL در سطح منطق خاص قبل از قدرت انجام می شود.هر حالت از پین ها و پروتکل های مختلف استفاده می کند ، بنابراین باید سازگاری با ابزارهای طراحی و حافظه پیکربندی خود را تأیید کنید.انتخاب درست در اینجا یک فرآیند پیکربندی صاف را تضمین می کند.

2. Power را اعمال کرده و دستگاه را اولیه کنید

در مرحله بعد ، ریل های هسته FPGA و I/O را در محدوده ولتاژ مشخص کنید.در حین راه اندازی ، پین NCONFIG را کم نگه دارید تا دستگاه را دوباره تنظیم کنید تا ولتاژهای تأمین پایدار شوند.پس از پایدار بودن ، با رانندگی پین NSTATUS ، تنظیم مجدد را آزاد می کنید و دستگاه آمادگی را نشان می دهد.این تضمین می کند که FPGA قبل از شروع پیکربندی به درستی تنظیم می شود.

3. BITSTREAM پیکربندی را انتقال دهید

در این مرحله ، پرونده داده پیکربندی (BitStream) را با استفاده از طرح انتخاب شده خود به FPGA ارسال می کنید.در حالت سریال فعال یا سریال منفعل ، Bitstream از یک دستگاه حافظه خارجی تهیه می شود ، در حالی که JTAG امکان برنامه نویسی مستقیم از طریق کابل را فراهم می کند.دستگاه به طور مداوم در داده های پیکربندی تا زمانی که کامل شود ، می خواند.نرم افزار طراحی شما این bitstream را تولید می کند تا مطابق با الزامات منطق شما باشد.

4. پیکربندی موفق را تأیید کنید (Conf_done)

هنگامی که FPGA بارگیری را به پایان رساند ، پین Conf_done را ادعا می کند تا نشان دهد که داده های پیکربندی با موفقیت دریافت شده اند.در عین حال ، دستگاه اولیه سازی داخلی مانند پاکسازی رجیسترها و فعال کردن I/O را انجام می دهد.اگر Conf_Done نتواند زیاد پیش برود ، معمولاً به این معنی است که داده های پیکربندی یا تنظیم خطایی دارد.تماشای این پین ساده ترین راه برای تأیید کامل روند است.

5. تنظیم مجدد در سیستم اختیاری را انجام دهید

در آخر ، شما می توانید FPGA را بدون حذف آن از صفحه ، به روز کنید یا دوباره برنامه ریزی کنید.با استفاده از JTAG یا یک کنترلر تعبیه شده ، می توانید یک Bitstream جدید را مستقیماً بارگیری کنید ، که برای به روزرسانی های سیستم عامل مفید است.این انعطاف پذیری به شما امکان می دهد حتی پس از استقرار سیستم خود را اصلاح ، اشکال زدایی یا به روزرسانی کنید.این تضمین می کند که طراحی مبتنی بر FPGA شما می تواند به مرور زمان با تغییر نیازها سازگار شود.

مزایا و مضرات EP1C4F400C8

مزایا

• انتخاب مقرون به صرفه برای طرح های میان رده

• تعداد I/O زیاد در مقایسه با دستگاه های چگالی مشابه

• ولتاژ انعطاف پذیر و پشتیبانی استاندارد I/O

• از ابزارها و مستندات بالغ پشتیبانی می شود

• مصرف انرژی کمتری نسبت به نسل های قدیمی تر FPGA

معایب

• منسوخ شده با در دسترس بودن طولانی مدت محدود

• منطق و ظرفیت حافظه پایین در مقابل FPGA های مدرن

• سرعت عملیاتی آهسته تر و عملکرد I/O

• برای پیکربندی در زمینه قدرت به حافظه خارجی نیاز دارد

• فاقد ویژگی های پیشرفته مانند بلوک های DSP و فرستنده های پر سرعت است

ابعاد بسته بندی EP1C4F400C8

|

نوع |

پارامتر |

|

نوع بسته بندی |

FBGA (آرایه شبکه توپ خوب) |

|

شمارش توپ |

400 |

|

زمین توپ (E) |

1.0 میلی متر (معمولی برای Cyclone EP1C4F400) |

|

قطر توپ (ب) |

0.45 میلی متر (اسمی) |

|

اندازه بسته (D × E) |

21 میلی متر × 21 میلی متر |

|

ارتفاع بسته (A) |

2.40 میلی متر (حداکثر) |

|

ضخامت بستر (A2) |

0.40 میلی متر پوند |

|

ضخامت کلاه قالب (A3) |

1.90 میلی متر پوند |

|

ارتفاع توپ (A1) |

0.25 میلی متر (اسمی) |

|

گوشه A1 پین |

برای جهت گیری مشخص شده است |

|

طرح آرایه |

شبکه 20 × 20 (با توپ های گوشه ای از دست رفته) |

|

نصب |

سوار بر سطح (SMD) |

تولید کننده EP1C4F400C8

EP1C4F400C8 در ابتدا توسط ساخته شده است شرکت Altera، پیشگام در دستگاه های منطق قابل برنامه ریزی و فناوری FPGA.در سال 2015 ، Altera توسط شرکت اینتل، و خط تولید بخشی از گروه راه حل های قابل برنامه ریزی اینتل (PSG) شد.امروز ، اینتل ضمن تمرکز توسعه بر روی خانواده های جدیدتر FPGA ، از تداوم کاربران موجود و پیشبرد نوآوری در منطق قابل برنامه ریزی ، از این دستگاه های Legacy Altera پشتیبانی می کند.

پایان

EP1C4F400C8 به عنوان یک FPGA مقرون به صرفه و همه کاره است که عملکرد کاملی را برای طرح های میان رده ارائه می دهد.با 4000 عنصر منطقی خود ، حافظه تعبیه شده ، پشتیبانی گسترده I/O و سازگاری با استانداردهای ولتاژ و رابط چندگانه ، انعطاف پذیری را در برنامه های متنوع فراهم می کند.معماری ، فرآیند برنامه نویسی و قابلیت استفاده گسترده در DSP ، سیستم های تعبیه شده و کسب داده ها با وجود وضعیت میراث خود ، آن را به یک انتخاب عملی تبدیل می کند.در حالی که فاقد ویژگی های پیشرفته موجود در دستگاه های جدیدتر است و در دسترس بودن طولانی مدت با محدودیت طولانی مدت است ، اما گزینه ای قابل اعتماد است که به دنبال راه حل های اثبات شده در طرح های مقیاس پذیر FPGA است.

برگه داده PDF

برگه های داده EP1C4F400C8:

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

سوالات متداول [FAQ]

1. برای برنامه ریزی EP1C4F400C8 چه ابزاری لازم است؟

شما به نرم افزار کوارتوس اینتل (قبلاً Altera Quartus II) به همراه کابل برنامه نویسی پشتیبانی شده مانند USB-Blaster نیاز دارید.این ابزارها به شما امکان می دهند تا bitstream را ایجاد کرده و آن را در FPGA بارگذاری کنید.

آیا می توان EP1C4F400C8 برنامه های PCI را مستقیماً کنترل کرد؟

بله ، این رعایت داخلی برای استانداردهای PCI (33/66 مگاهرتز ، 32/64 بیتی) است ، و این امر را برای ادغام سیستم مبتنی بر PCI بدون نیاز به منطق پل اضافی مناسب می کند.

3. چه اتفاقی می افتد اگر EP1C4F400C8 در طول پیکربندی شکست بخورد؟

در صورت عدم موفقیت پیکربندی ، پین conf_done اثبات بالایی نخواهد داشت.این معمولاً به خطایی در پرونده bitstream ، توالی ولتاژ یا تنظیم پین اشاره دارد و باید در جریان طراحی شما دوباره بررسی شود.

4. آیا می توان EP1C4F400C8 را مستقیماً با حافظه DDR رابط کرد؟

این چندین استاندارد I/O را پشتیبانی می کند اما دارای رابط های DDR بومی مانند FPGA های مدرن نیست.ملاحظات طراحی اضافی یا اجزای پل سازی ممکن است مورد نیاز باشد.

5. EP1C4F400C8 چگونه با FPGA های جدیدتر مقایسه می شود؟

در مقایسه با دستگاه های مدرن ، EP1C4F400C8 دارای سرعت کمتری ، چگالی منطق کمتر و ویژگی های پیشرفته کمتری است.با این حال ، این یک انتخاب مقرون به صرفه برای طرح های پایدار و میان رده است که در آن عملکرد برش لازم نیست.

نمای کلی CPLD EPM3256AFC256-7: ویژگی ها ، Pinout ، برنامه نویسی و برنامه ها

در 2025/10/3

سوئیچ آنالوگ ADG432BR IC: مشخصات ، pinout ، گزینه های دیگر و برگه داده

در 2025/10/2

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147780

-

pinout uSB-C و ویژگی های

در 2000/04/18 112041

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111352

-

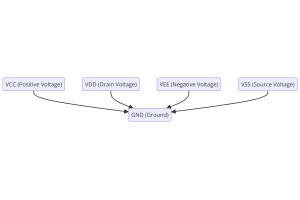

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83798

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79604

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66982

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 63113

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63048

-

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54097

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52198