رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

تجزیه و تحلیل معماری نهایی پردازنده های رایانه از پیچیدگی های عملکرد و عملکرد آنها رونمایی می کند.از جمله تأثیرگذارترین طرح های پردازنده می توان به معماری رایانه ای مجموعه دستورالعمل (CISC) و معماری مجموعه دستورالعمل مجموعه (RISC) اشاره کرد.هر یک رویکردهای منحصر به فرد برای اجرای دستورالعمل ، راندمان برنامه نویسی و طراحی سخت افزار ارائه می دهند.این مقاله به بررسی پیچیدگی های معماری CISC می پردازد ، با تأکید بر مجموعه آموزش گسترده آن که برنامه نویسی را هنگام ارائه چالش های سخت افزاری ساده می کند.همچنین به رویکرد RISC ساده ، که عملکرد را از طریق یک مجموعه دستورالعمل ساده و کارآمد بهینه می کند ، حفر می شود.سرانجام ، این پست نشان می دهد که چگونه پردازنده های مدرن به طور فزاینده معماری های ترکیبی را اتخاذ می کنند ، و نقاط قوت CISC و RISC را برای رفع نیازهای محاسباتی متنوع ترکیب می کنند.کاتالوگ

نمای کلی از CISC

معماری یک پردازنده رایانه در اطراف اجرای طیف متنوعی از دستورالعمل ها یا میکرواستراسیون ها ، هر یک برای انجام کارهای خاص طراحی شده است.در حالی که یک مجموعه دستورالعمل جامع تر می تواند برنامه نویسی را برای ریزپردازنده بصری تر کند ، اما ممکن است موانع عملکرد بالقوه را نیز معرفی کند.معماری مجموعه دستورالعمل مجموعه Computer (CISC) به دلیل جمع آوری گسترده دستورالعمل ها ، از جمله موارد پیچیده ای که تجربه برنامه نویسی را در مقایسه با معماری های جایگزین ساده می کند ، مشخص است.هر کار ، چه ساده و چه پیچیده ، با یک دستورالعمل منحصر به فرد جفت می شود ، که میزان کدگذاری مورد نیاز را کاهش می دهد.با این حال ، این طراحی پیچیده می تواند چالش های قابل توجهی در توسعه CPU و مدار واحد کنترل مرتبط داشته باشد.

معماری CISC با انتخاب گسترده ای از ریزساختاری ها که توسعه برنامه را برای پردازنده تسهیل می کند ، متمایز می شود.این میکرواستراسیون ها ، که اغلب به زبان مونتاژ بیان می شوند ، کارکردهای خاصی را جایگزین می کنند که به طور سنتی توسط نرم افزار با سیستم های آموزش سطح سخت افزاری انجام می شدند.این تغییر نه تنها حجم کار را برای شما روشن می کند بلکه اجرای همزمان عملیات سطح پایین را در طی هر چرخه دستورالعمل امکان پذیر می کند و سرعت کلی اجرای رایانه را افزایش می دهد.

فرکانس استفاده از دستورالعمل در مجموعه دستورالعمل CISC ، عدم تعادل چشمگیر را به نمایش می گذارد.تقریباً 20 ٪ از دستورالعمل ها معمولاً مورد استفاده قرار می گیرند ، حدود 80 ٪ از کل برنامه برنامه را تشکیل می دهند ، در حالی که 80 ٪ باقیمانده به ندرت به کار می روند و تنها 20 ٪ برنامه نویسی را به خود اختصاص می دهد.این مشاهده با یک اصل وسیع تر که در زمینه های مختلف مشاهده می شود طنین انداز است: انتخاب کوچکی از ابزارها یا روشها اغلب اکثر نتایج را تولید می کند.

مقایسه CISC و RISC

معماری کاهش یافته مجموعه دستورالعمل (RISC) به دلیل مجموعه دستورالعمل ساده خود ، که هدف آن تقویت کارایی پردازنده است ، مشخص شده است.با این حال ، این طرح به یک رویکرد پیچیده تر برای برنامه نویسی خارجی نیاز دارد.RISC با تمرکز بر روی دستورالعمل های ساده متداول ، از عوارضی که اغلب با دستورات پیچیده تر همراه هستند ، جلوگیری می کند.

• معماری RISC طول دستورالعمل را استاندارد می کند.

• این فرمت های دستورالعمل را ساده تر می کند ، در درجه اول با تکیه بر منطق کنترل.

• این انتخاب طراحی نیاز به کنترل میکروکد را از بین می برد و در نتیجه سرعت عملیاتی سریعتر ایجاد می شود.

منشأ RISC را می توان به تحقیقات پیشگامانه انجام شده توسط جان کوک در IBM بازگرداند.یافته های وی حاکی از آن است که تنها حدود 20 ٪ دستورالعمل های رایانه تقریباً 80 ٪ از حجم کار محاسباتی را تشکیل می دهد.این بینش وزن قابل توجهی دارد ، نشان می دهد که با بهینه سازی دستورالعمل های متداول ، می توان به پیشرفت های گسترده ای رسید.در نتیجه ، سیستم های RISC غالباً از سیستم های Complex Complet Computer (CISC) استفاده می کنند ، و با اصل مشهور 80/20 که از توسعه معماری RISC آگاه است ، هماهنگ است.

در حالی که RISC دارای چندین مزیت است ، اما کاملاً جایگزین معماری CISC نمی شود.هر نوع نقاط قوت متمایز خود را دارد و اختلافات بین آنها با گذشت زمان کمتر نشان داده می شود.در عمل معاصر ، بسیاری از CPU های مدرن عناصری را از RISC و CISC در خود جای می دهند و این روند رو به رشد به سمت معماری های ترکیبی را نشان می دهد.به عنوان مثال ، CPU های آموزشی فوق العاده طولانی (ULIW) این ترکیب را نشان می دهد ، و مزایای هر دو معماری را برای تولید یک واحد پردازش سازگار تر ادغام می کند.این همجوشی نه تنها باعث افزایش عملکرد می شود بلکه انعطاف پذیری را در برنامه نویسی نیز معرفی می کند و امکان طیف گسترده تری از برنامه ها را فراهم می آورد.

دربارهی ما

ALLELCO LIMITED

ادامه مطلب

پرس و جو سریع

لطفاً یک سؤال ارسال کنید ، ما بلافاصله پاسخ خواهیم داد.

فن آوری بسته بندی Flat Flat Square (QFP): طراحی ، برنامه ها و چالش ها

در 2024/12/30

دستگاه های منطقی قابل برنامه ریزی قابل برنامه ریزی (EPLDS): راهنمای طراحی و برنامه ها

در 2024/12/30

پست های محبوب

-

رایانه های مجموعه دستورالعمل پیچیده: چگونه آنها محاسبات را تغییر دادند؟

در 8000/04/18 147750

-

pinout uSB-C و ویژگی های

در 2000/04/18 111921

-

با استفاده از Xilinx Simulation Simulation Primitives: یک راهنمای جامع برای طراحی و شبیه سازی FPGA

در 1600/04/18 111349

-

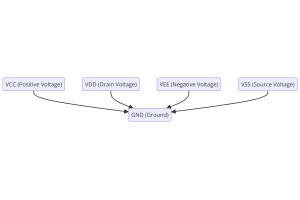

ولتاژ منبع تغذیه در الکترونیک: معنی VCC، VDD، VEE، VSS و GND

در 0400/04/18 83714

-

راهنمای اتصال RJ45: Pinout ، سیم کشی ، انواع کابل و موارد استفاده

در 1970/01/1 79502

-

راهنمای نهایی برای کدهای رنگ سیم در سیستم های برقی مدرن

روشی که سیستم های برقی ما از رنگ ها استفاده می کنند فقط به نظر نمی رسد.در حال حاضر هر رنگ سیم یک عملکرد خاص را نشان می دهد ، و در هنگام نصب و نگهداری ، شناسایی و کنترل صحیح اجزای الکتریکی را آسان ت...در 1970/01/1 66872

-

کیفیت (س) فاکتور: معادلات و برنامه ها

ضریب کیفیت یا "Q" هنگام بررسی چگونگی کار سلف و طنین انداز در سیستم های الکترونیکی که از فرکانس های رادیویی استفاده می کنند (RF) مهم است."Q" اندازه گیری می کند که چگونه یک مدار از دست دادن انرژی به ...در 1970/01/1 63005

-

راهنمای دریچه Purge: عملکرد ، علائم ، آزمایش و جایگزینی برای عملکرد بهینه موتور

دریچه پاکسازی بخش مهمی از سیستم خودرو است که به تمیز نگه داشتن هوا با مدیریت بخارات سوخت قبل از فرار به جو کمک می کند.این نه تنها با کاهش آلودگی به محیط زیست کمک می کند بلکه باعث می شود ماشین بهتر ...در 1970/01/1 62954

-

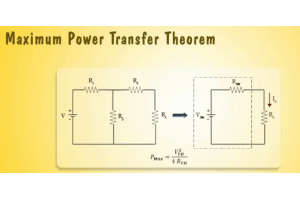

دستیابی به عملکرد اوج با حداکثر قضیه انتقال قدرت

حداکثر قضیه انتقال نیرو توضیح می دهد که چگونه انرژی از یک منبع ، مانند باتری یا ژنراتور ، به یک بار متصل می رود.این وضعیت دقیق را نشان می دهد که بار بیشترین قدرت را دریافت می کند.این مقاله شامل آنچ...در 1970/01/1 54078

-

مشخصات باتری A23 و سازگاری

باتری A23 یک باتری کوچک و استوانه ای با ولتاژ بالا است.همچنین به آن 23A ، 23AE یا MN21 گفته می شود ، با 12 ولت و بسیار بالاتر از باتری های AA یا AAA اجرا می شود.طراحی ویژه آن باعث می شود ت...در 1970/01/1 52092